# Министерство общего и профессионального образования Российской Федерации

Санкт-Петербургская государственная академия холода и пищевых технологий

Кафедра электротехники

# ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

Методические указания для самостоятельного изучения дисциплины "Электротехника и основы электроники" для студентов всех специальностей

## УДК 621.3

Евстигнеев А. Н. , Кузьмина Т.Г. , Новотельнова А. В. Основы цифровой электроники: Метод. указания для сомостоятельного изучения дисциплины "Электротехника и основы электроники" для студентов всех спец. - СПб.: СПбГАХПТ , 1999. - 41 с.

Содержит основные сведения о современной элементарной базе цифровых электронных схем.

Ил. -25, табл. -7, библиогр. -10 назв.

#### Рецензент

Канд. техн. наук, доцент А. И. Васильев

Одобрены к изданию советом факультета техники пищевых производств

(C)

Санкт-Петербургская государственная академия холода и пищевых технологий, 1999

## **ВВЕДЕНИЕ**

Любая электронная схема от простейшего выпрямителя до сложнейшей ЭВМ предназначена для обработки электрического сигнала: усиление (масштабирование), выпрямление, сглаживание (изменение формы, запоминание, суммирование и пр.). По способу представления обрабатываемого сигнала электронные устройства принято подразделять на аналоговые и цифровые.

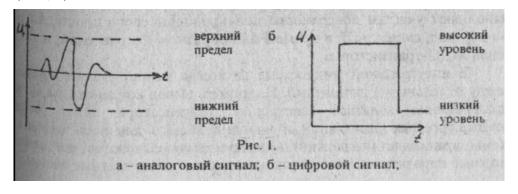

В аналоговых устройствах используются переменные, изменяющие свое значение в определенном диапазоне значений между верхним и нижним пределами. Это естественно, когда обрабатываемые сигналы являются непрерывными по своей природе или представляют собой непрерывно изменяющиеся напряжения, поступающие от измерительных приборов (например, от устройств для измерения температуры, дав- ления, влажности). Пример аналогового сигнала U(t) приведен на рис. 1, а.

Однако входной сигнал по своей природе может быть и дискретным, например, импульсы в детекторе частиц или "биты" информации, поступающие от ключа, клавиатуры или ЭВМ. В подобных случаях удобно использовать цифровую электронику, т. е. схемы, которые имеют дело с информацией, представленной в виде "единиц" и "нулей". Цифровые переменные имеют только два уровня (рис. 1, б). Эти уровни напряжения называют верхним и нижним, или обозначают терминами "истина" и "ложь", которые связаны с булевой логикой, или "включено" и "выключено", которые отражают состояние релейной системы, а чаще "нулем" и "единицей".

Благодаря высокой эффективности цифровые методы широко используются для передачи, отбора и запоминания информации, даже в тех случаях, когда входные и выходные данные имеют непрерывную или аналоговую форму. В этом случае информацию необходимо преобразовывать при помощи цифро-аналоговых (ЦАП) и аналогово-цифровых преобразователей (АЦП).

а – аналоговый сигнал; б – цифровой сигнал;

## 1. ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ

Интегральная микросхема — это микроэлектронное изделие, выполняющее определенную функцию преобразования и обработки сигнала и имеющее не менее пяти элементов (транзисторов, диодов, резисторов, конденсаторов), которые нераздельно связаны и электрически соединены между собой так, что устройство рассматривается как единое целое.

Высокая надежность и качество в сочетании с малыми размерами, массой и низкой стоимостью интегральных микросхем обеспечили их широкое применение во многих отраслях народного хозяйства.

По конструктивно-технологическим признакам различают пленочные, полупроводниковые и гибридные микросхемы.

Пленочные микросхемы изготавливают посредством послойно- го нанесения на диэлектрическое основание (подложку) пленок раз-личных материалов с одновременным формированием транзисторов, диодов и т. п. Пленочные микросхемы делятся на тонкопленочные (тол-щина пленки до 1мкм) и толстопленочные.

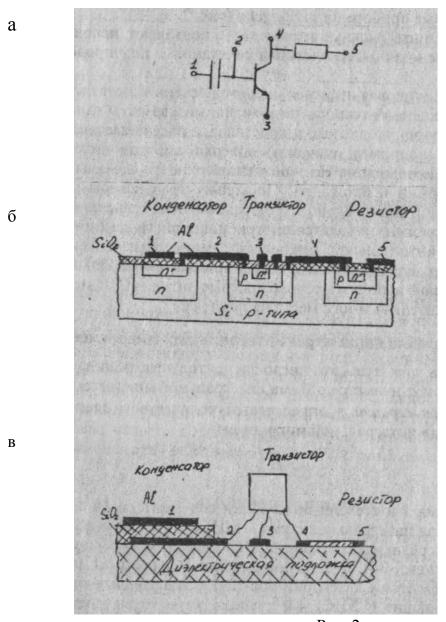

Полупроводниковая интегральная микросхема — это интегральная микросхема, все элементы и межэлектродные соединения которой выполнены в объеме и на поверхности полупроводника (рис. 2 а, б).

При изготовлении полупроводниковых интегральных микросхем обычно используют планарную технологию.

Активные и пассивные элементы полупроводниковой интег-ральной микросхемы избирательно формируют монокрис-талле одном полупроводника. Соединение элементов между собой в полупро-водниковой интегральной микросхеме может быть выполнено как в объеме, так и на поверхности монокристалла полупроводника путем создания на окисленной поверхности полупроводника токоведущих до-рожек, например, методом вакуумного напыления металла. В качестве конденсаторов в микросхемах используют обратно смещенные *р-п-*пе-реходы или конденсаторные структуры Si- $SiO_2$ -металл. Роль резисторов выполняют участки поверхности полупроводникового кристалла или p-n-переход, смещенный в прямом или обратном направлении, а также канал МДП-транзисторов.

В интегральной микросхеме не всегда можно указать границу между Например, отдельными элементами. вывод конденсатора может электродом одновременно конденсатора. являться малых межэлектродных расстояний и наличия общего для всех элементов схемы кристалла (подложки) в микросхемах создаются достаточно сложные паразитные связи, а так же появляются паразитные элементы, которые, как правило, ухудшают все параметры микросхемы, как функционального узла радиоэлектронной аппаратуры.

Рис. 2

а – эквивалентная схема; б – структура полупроводниковой интегральной микросхемы; в – структура гибридной интегральной микросхемы

Гибридная интегральная микросхема — это интегральная микро-схема пассивные элементы которой выполнены посредством нанесения различных пленок на поверхность диэлектрической подложки из стекла, керамики или ситалла, а активные элементы — навесные полупроводниковые приборы без корпусов (рис. 2, в).

Гибридные интегральные микросхемы позволяют использовать преимущества пленочной технологии в сочетании с полупроводниковой технологией. Полупроводниковая интегральная микросхема может быть изготовлена по совмещенной технологии — активные элементы выполнены в объеме полупроводникового монокристалла, а пассивные элементы — на защищенной (например, окислом) поверхности монокристалла в тонкопленочном исполнении. На этой же поверхности сделаны и токопроводящие дорожки и площадки. Поскольку транзисторы и диоды полупроводниковой интегральной микросхемы, изготовленной по совмещенной технологии, находятся внутри монокристалла (подложки), размеры такой интегральной микросхемы могут быть значительно уменьшены по сравнению с размерами гибридной интегральной микросхемы, в которой используются дискретные активные элементы, занимающие сравнительно много места на подложке.

## 1.1. Основные параметры интегральных микросхем

*Плотность упаковки* — это число элементов электронной схемы в одном кубическом сантиметре объема интегральной микросхемы.

Ствень интеграции  $\chi$  определяется количеством элементов n, входящих в состав интегральной микросхемы.

$$\chi = lg n$$

Микросхема 1-й степени интеграции содержит до 10 элементов (маломасштабная интегральная схема — МИС). Микросхема 2-й степени интеграции (среднемасштабная — СИС) содержит от 10 до 100 элементов. Микросхема 3-й степени интеграции содержит от  $10^2$  до  $10^3$  элементов и относится к категории больших интегральных микросхем (БИС). Сверхбольшие (СБИС) 4-й степени интеграции имеют более 1000 элементов (табл. 1).

| Уровень сложности ИС | Количество интегрированных элементов | Параметры функционального<br>назначения ИС                                            |

|----------------------|--------------------------------------|---------------------------------------------------------------------------------------|

| МИС                  | ≤ 10                                 | Биполярные ячейки, простые логические элементы, дифференциальные усилительные каскады |

| СИС                  | 10–100                               | Триггеры, регистры, сумматоры, операцион- ные усилители, коммутаторы                  |

| БИС                  | 100–1000                             | Полупроводниковые запоминающие и ариф-метико-логические устройства                    |

| СБИС                 | > 1000                               | Микропроцессоры, однокристальные микро-<br>ЭВМ, аналого-цифровые преобразователи      |

## 1.2. Серии и семейства серий интегральных схем

Серия — это комплект из нескольких типов интегральных схем, имеющих единое конструктивно-технологическое исполнение и предназначенных для совместного применения в аппаратуре. Интегральные схемы, входящие в серию, имеют единые эксплуатационные показатели и используются как совместимые наборы деталей, пригодные для создания электронной аппаратуры любой степени сложности.

Серии интегральных схем, совместимые друг с другом по логическим уровням, условиям эксплуатации и конструктивным показателям, могут образовывать *семейства серий интегральных схем*.

#### 2. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Логические и запоминающие элементы составляют основу устройств цифровой обработки информации — вычислительных машин, цифровых измерительных приборов и устройств автоматики. Логические элементы выполняют простейшие логические операции над цифровой информацией: преобразуют по определенным правилам входную информацию в выходную. Операции, используемые при обработ- ке цифровой информации, основаны на двоичной системе счисления, представляющей информацию в виде слов — комбинаций символов 1 и 0.

Обработка цифровой информации логическими элементами производится по законам и правилам алгебры логики, разработанной в XIX веке английским ученым Дж. Булем.

Логические преобразования двоичных сигналов включают три элементарные операции:

- логическое сложение (дизъюнкцию) или операцию ИЛИ

$$F = x_1 + x_2 + ... + x_n$$

;

– логическое умножение (конъюкцию) или операцию И

$$F = x_1 \cdot x_2 \cdot \ldots \cdot x_n$$

– логическое отрицание (инверсию) или операцию НЕ

$$F = x$$

Определение этих операций дается с помощью таблиц истин-ности, содержащих перечисление всех возможных сочетаний (наборов) входных переменных (входных слов).

Каждая простая логическая функция может быть технически реализована простыми элементами, к которым относятся элементы И, ИЛИ, НЕ и их комбинации.

В табл. 2 приведены условные обозначения логических элементов и таблицы истинности.

Из простых элементов можно составить сколь угодно сложные логические устройства, например, счетчики импульсов, регистры, сумматоры, блоки памяти и т. п.

На практике применяют комбинированные элементы, реали- зующие две логические операции, например, элементы И - HE и UЛИ - HE. Они называются функционально полными, т. к. позволяют реализовать любую логическую функцию. Например, имея набор элементов U - HE, можно построить схему UЛИ.

| Наименование | Условное    | Выражение              | Таблицы истинности    |   |   |   |   |

|--------------|-------------|------------------------|-----------------------|---|---|---|---|

| функции      | графическое | функции                | x <sub>1</sub>        | 0 | 0 | 1 | 1 |

| Bar Milk     | обозначение |                        | <i>x</i> <sub>2</sub> | 0 | 1 | 0 | 1 |

| или          | XI I y      | $y=x_1+x_2$            | у                     | 0 | 1 | 1 | 1 |

| И            | X1 8 y      | $y=x_1 x_2$            | у                     | 0 | 0 | 0 | 1 |

| НЕ           | Xy y        | $y=\overline{x_1}$     | у.                    | 1 | 1 | 0 | 0 |

| или – не     | XI I y      | $y=\overline{x_1+x_2}$ | у                     | 1 | 0 | 0 | ( |

| И – НЕ       | Xe & y      | $y=x_1x_2$             | у                     | 1 | 1 | 1 | ( |

Таблица 2

| Наименование | Условное    | Выражение        | Таблицы истинности |   |   |   |   |

|--------------|-------------|------------------|--------------------|---|---|---|---|

| функции      | графическое | функции          | $x_1$              | 0 | 0 | 1 | 1 |

|              | обозначение |                  | $x_2$              | 0 | 1 | 0 | 1 |

| или          |             | $y = x_1 + x_2$  | У                  | 0 | 1 | 1 | 1 |

| И            |             | $y=x_1\cdot x_2$ | у                  | 0 | 0 | 0 | 1 |

| НЕ       | $y = x_1$                   | у | 1 | 1 | 0 | 0 |

|----------|-----------------------------|---|---|---|---|---|

| ИЛИ – НЕ | $y = \overline{x_1 + x_2}$  | у | 1 | 0 | 0 | 0 |

| И – НЕ   | $y=\overline{x_1\cdot x_2}$ | У | 1 | 1 | 1 | 0 |

Элемент И – НЕ (штрих Шеффера) выполняет операцию

$$F = \overline{x_1 \cdot x_2 \cdot x_3 \cdot \dots \cdot x_n}$$

Элемент ИЛИ – НЕ (стрелка Пирса) выполняет операцию

$$F=x_1 + x_2 + x_3 + ... + x_n$$

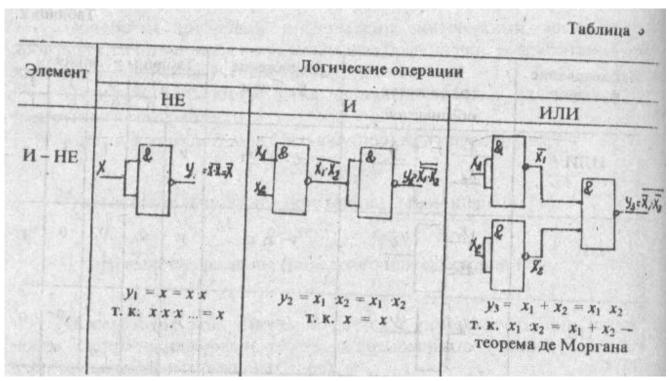

Примеры использования функционально полных элементов приведены в табл. 3, где показано, как набором элементов И-HE можно реализовывать функции И, ИЛИ, HE.

Таблица 3

| Элемент | Логические операции                                       |                                                     |                                                                                         |  |  |

|---------|-----------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

|         | HE                                                        | И                                                   | ИЛИ                                                                                     |  |  |

| И – НЕ  |                                                           |                                                     |                                                                                         |  |  |

|         | $y_1 = x = x \cdot x$ T. K. $x \cdot x \cdot x \dots = x$ | $y_2 = x_1 \cdot x_2 = x_1 \cdot x_2$ T. K. $x = x$ | $y_3 = x_1 + x_2 = x_1 \ x_2$<br>т. к. $x_1 \cdot x_2 = x_1 + x_2$ — теорема де Моргана |  |  |

Реализация логических устройств на базе комбинированных элементов упрощает компановку и ремонт устройств.

## 3. СХЕМНЫЕ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Основой для построения узлов импульсной и цифровой техники служат полупроводниковые ключевые схемы. Ключевая схема (ключ) позволяет подключать нагрузку к источнику или отключать ее и, таким обра-

зом, коммутировать ток в нагрузке. В качестве электронных ключей применяют диоды, транзисторы, тиристоры и некоторые другие электронные приборы.

## 3.1. Ключевой режим работы биполярного транзистора

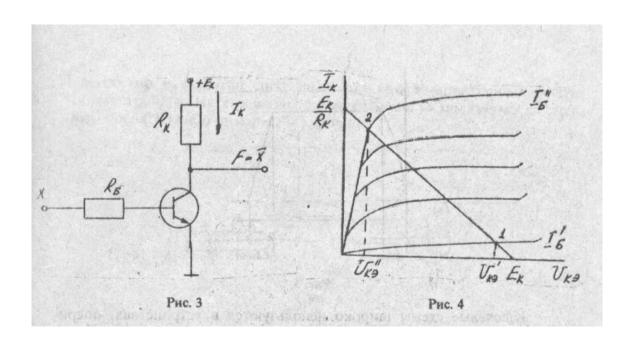

Простейший транзисторный ключ — каскад на биполярном транзисторе, включенный по схеме с общим эмиттером, представлен на рис. 3. Выходное сопротивление транзистора по постоянному току со стороны электродов коллектор-эмиттер может изменяться в широких пределах в зависимости от положения рабочей точки на вольт-амперной характеристике (рис. 4).

Точка 1 на рис. 4 соответствует режиму отсечки (состояние "выключено"), в котором падение напряжения на транзисторе  $V_{\rm K3}^{'}$  близко к напряжению источника питания  $E_{\rm K}$ . Точки  $I_{\rm K}$  и  $I_{\rm B}$  при этом минимальны и равны обратному току коллекторного перехода  $I_{\rm KO}$ .

Точка 2 (состояние "включено") соответствует режиму насыщения. При этом через транзистор протекает максимально возможный при данных  $E_{\rm K}$  и  $R_{\rm K}$  ток, практически равный  $E_{\rm K}/R_{\rm K}$ , т.е. определяемый величиной нагрузочного сопротивления. Падение напряжения на транзисторе  $V_{\rm K9}$ " в этом случае минимально.

Для переключения транзистора из режима отсечки в режим насыщения необходимо обеспечить определенный ток базы  $I_{\rm B}$ ", для чего на эмит-

терный переход требуется подать соответствующее этому току напряжение  $U_{\mathrm{D}}$ .

Важнейшим показателем работы электронных ключей является их быстродействие, которое определяется скоростью протекания переходных процессов при переключении. Мгновенное переключение транзисторного ключа невозможно из-за инерционности свойств транзисто-ров, а также наличия паразитных реактивных элементов схемы и про-водников.

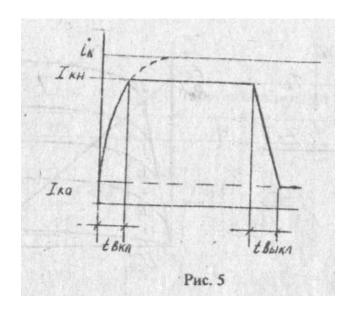

Переход транзистора из одного стационарного состояния в другое происходит с задержками времени  $t_{\rm вкл}$  и  $t_{\rm выкл}$  (рис. 5). Длительность фронта включения  $t_{\rm вкл}$  зависит от времени распространения носителей от эмиттера через базу к коллектору и значения коллекторной емкости. Это время уменьшается при увеличении тока базы.

Задержка выключения  $t_{\text{выкл}}$  связана с тем, что под действием выключающего сигнала происходит рассасывание заряда, накопивше-гося в базе при насыщении транзистора.

Таким образом, быстродействие транзисторного ключа зависит от частотных свойств используемого транзистора и параметров импульса базового тока. Порядок величин задержек составляет от долей единицы до микросекунд.

Рис. 5

Ключевые схемы широко используются в устройствах, оперирующих с информацией, представленной в цифровой форме. В частности, их применяют в элементах, выполняющих простейшие логические операции. Переключение основной схемы из одного состояния в другое производится с по-

мощью управляющих сигналов, подаваемых на ее вход. Эти сигналы могут быть представлены в виде ступенчатого или импульсного напряжения.

В логических устройствах сигнал может принимать только два значения: логического нуля и логической единицы. Если логической единице соответствует высокий потенциальный уровень, а логическому нулю — низкий, такую логику называют положительной (позитивной). В противном случае логика называется отрицательной (негативной). Интегральные логические элементы изготавливаются в основном для работы в позитивной логике.

Рассмотренный нами простейший транзисторный ключ выполняет логическую операцию отрицания (операцию НЕ). Высокому уровню напряжения на входе ключа ("1") соответствует низкий уровень напряжения на его выходе ("0"), и наоборот.

В совокупности с другими элементами транзисторные ключи могут выполнять более сложные функции.

## 3.2. Транзисторно-транзисторная логика (ТТЛ)

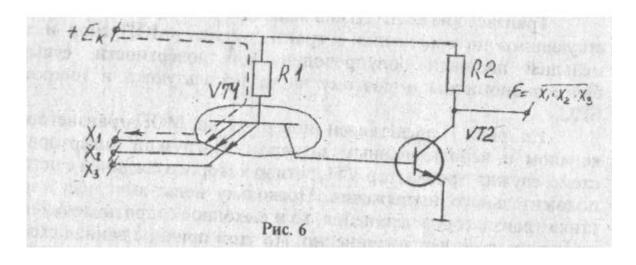

Простейшая ключевая схема имеет один управляющий вход и один выход. В общем случае число входов и выходов может быть больше. На рис. 6 приведена схема логического элемента И – НЕ, построенная на основе транзисторного ключа. В состав элемента входит ключевая схема на транзисторе VT2. Управление схемой производится с помощью многоэмиттерного транзистора VT1. Многоэмиттерный транзистор разработан специально для микроминиатюрных логиче-ских устройств. На его входы (эмиттеры) могут подаваться сигналы высокого ("1") либо низкого ("0") уровня.

Рис. 6

Рассмотрим принцип работы схемы. Если на все входы (в данном случае на три) подан высокий положительный потенциал ( $x_1 = x_2 = x_3 = 1$ ), то транзистор VT1 закрывается, потенциал коллекто-ра VT1 близок к напряжению  $+E_{\rm K}$ , что приводит к отпиранию транзистора VT2. Напряжение на выходе VT2 устанавливается низким, т. е. выходной сигнал соответствует логическому нулю (F = 0).

При наличии на одном из входов логического нуля, например,  $x_1 = 0$ , VT1 открывается. На коллекторе транзистора VT1 в этом режи-ме устанавливается низкий потенциал, и что приводит к закрытию транзистора VT2. На выходе устанавливается высокий потенциал, соответствующий логической единице, т.е. при  $x_1 = 0$  F = 1 при любом состоянии входов  $x_2$  и  $x_3$ . Таким образом схема реализует функцию 3И - HE.

## 3.3. Логические элементы на основе полевых транзисторов

## 3.3.1. МОП-транзисторная логика на ключах одного типа проводимости

Одним из основных достоинств полевых транзисторов с изолированным затвором (МОП-транзисторов) по сравнению с биполярным является более высокая технологичность и возможность изготовления на одной подложке большого числа приборов с идентичными парамет-рами. Кроме того, полевые транзисторы имеют очень высокое входное сопротивление и практически не потребляют мощности по входной (затворной) цепи.

Если логические элементы на базе полевых транзисторов выпол-нены по интегральной технологии, то в качестве нагрузки ключевого транзистора с точки зрения упрощения технологии оказывается более выгодным использовать не резистор, а второй МОП-транзистор, у которого затвор и исток замкнуты.

Транзисторы nMOП-типа являются в 2–3 раза более быстродействующими по сравнению с транзисторами рМОП-типа и требуют меньшей площади полупроводниковой поверхности, существенно более экономичны и поэтому часто используются в микромощных БИС.

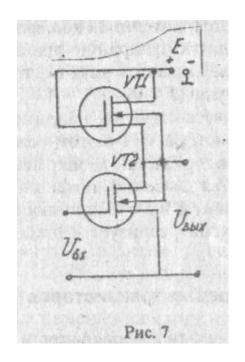

На рис. 7 представлен инвертор на МОП-транзисторах с п-каналом и использованным затвором. Нагрузкой инвертора в этой схеме служит транзистор VT1, затвор которого соединен с источником положительного напряжения. Поскольку вольт-амперная характеристика транзисторов нелинейна, то и выходное сопротивление при переключении изменяется нелинейно. По этой причине данная схема получила название ключа с нелинейной нагрузкой.

(управляющим). При низком входном потенциале (логический "0" на входе) транзистор VT2 закрыт, ток сто-ка  $I_{\rm c}=10^{-9}-10^{-10}$  А и менее,  $U_{\rm вых}\approx E_{\rm k}$  (логическая "1" на выходе). Когда на входе высокий потенциал (логическая "1" на входе), транзистор VT2 отпира-

Транзистор VT2 называется активным

Когда на входе высокий потенциал (логическая "1" на входе), транзистор VT2 отпирается, сопротивление канала резко падает и  $U_{\rm вых} \approx 0$  (логический "0" на выходе). Таким образом, в результате переключения транзистора выходное напряжение изменяется от  $E_{\rm k}$  до 0, т. е. схема реализует логическую функцию HE.

Рис. 7

# 3.3.2. МОП-транзисторная логика на комплиментарных транзисторах (КМОП-логика)

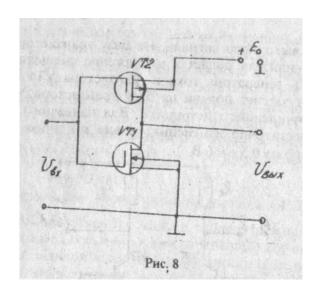

В основу построения данной логики положен комплиментарный транзисторный ключ, состоящий из последовательно соединенных полевых транзисторов с разным типом проводимости канала (комплиментарная пара) (рис. 8). В такой схеме коммутируются оба транзистора одновременно, так как затворы их соединены, т. е. на оба затвора поступает управляющий сигнал.

Рис. 8

При низком уровне входного сигнала открыт транзистор VT2 с p-каналом, а транзистор VT1 с n-каналом закрыт. При этом выходное напряжение, снимаемое со стоков обоих транзисторов, примерно равно  $E_0$ .

При высоком уровне входного сигнала открыт транзистор VT1, а транзистор VT2 закрыт, т. е. выходное напряжение близко к нулю. Схема реализует логическую функцию HE.

Основным достоинством этой схемы по сравнению с предыдущей является то, что в статическом состоянии один из транзисторов всегда закрыт, поэтому мощность, потребляемая от источника питания, очень мала. Расход мощности источника питания происходит только при переключении транзисторов и определяется в основном процессами перезаряда паразитных емкостей.

Недостатки схем на комплиментарных транзисторах – большое число элементов в логических схемах, усложнение технологии их изготовления – приводят к увеличению площади кристалла и стоимости изготовления по сравнению с интегральными схемами на однородных МОП-транзисторах.

## 3.4. Эмиттерно-связанная логика (ЭСЛ)

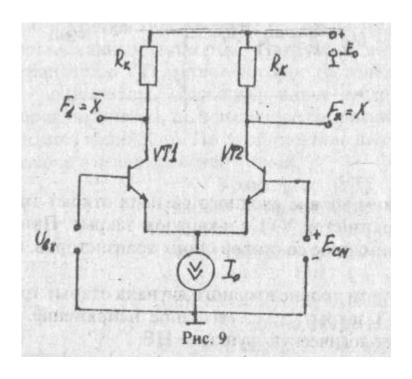

В логических элементах ЭСЛ в качестве ключа применяют транзисторные переключатели тока, производящие переключение тока от одной нагрузки к другой (рис. 9).

Принцип работы переключателя тока аналогичен принципу работы дифференциального усилительного каскада в режиме ограничения амплитуды выходного сигнала. На базу транзистора VT2 дифференциального усилителя подается напряжение смещение  $E_{\rm cm}$ , а переключение тока  $I_0$  генератора тока с транзистора VT1 на транзистор VT2 происходит за счет подачи на базу транзистора VT1 управляющего сигнала от внешнего источника. Для надежного переключения транзисторов достаточно изменения уровня входного управляющего сигнала примерно на  $0.5 \div 0.6$  В.

Рис. 9

Глубокая отрицательная обратная связь по току в схеме дифференциального каскада обусловливает то обстоятельство, что коллекторный ток каждого из транзисторов не может превысить ток генератора тока в эмиттерной цепи транзисторов. Выбором элементов схемы можно добиться выполнения условия  $I_0 < I_{\text{Кнас}}$ , поэтому транзисторы не переходят в режим насыщения и при переключении остаются в активном режиме. Эта особенность в сочетании с хорошими частот-ными свойствами транзисторов и самой схемы переключателей тока определяет ее высокое быстродействие. Время переключения таких схем может быть порядка нескольких наносекунд.

Связь между транзисторами в переключателе тока осуществ- ляется через генератор тока, включенный в неразветвленную цепь эмиттеров транзисторов. Это обстоятельство обусловливает название логических элементов, построенных на рассмотренном типе ключа, — эмитерно-связанная логика.

Рассматриваемая схема имеет два выхода:  $F_1$  и  $F_2$ . На выходе  $F_2$  фиксируется результат операции эквивалентности  $F_2 = x$ , а на выходе  $F_1$  операции НЕ  $F_1 = x$ .

Когда на логическом входе действует напряжение логической единицы (x = 1), транзистор VT1 открывается, а транзистор VT2 запирается. При этом на логическом выходе  $F_2$  имеем логическую единицу  $(F_2 = 1)$ , а на выходе  $F_1$  – логический ноль  $(F_1 = 0)$ .

Если напряжение на входе элемента становится равным напряжению логического ноля (x = 0), транзистор VT1 закрывается, а транзистор VT2 открывается. В этом случае на логическом выходе  $F_1$  имеем логическую единицу  $(F_1 = 1)$ , а на логическом выходе  $F_2$  – логи-ческий ноль  $(F_2 = 0)$ .

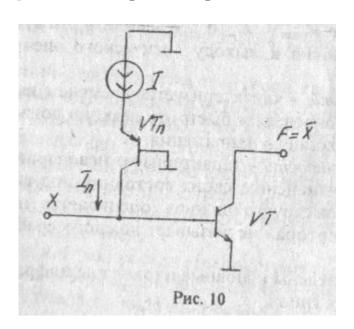

## 3.5. Интегральная инжекционная логика (ИІЛ-логика)

Схемы  $И^2 Л$  выпускаются только в интегральном исполнении.  $И^2 Л$ схемы работают с весьма малыми перепадами логических уровней и требуют минимальной площади поверхности полупроводниковой подложки. Показатель степени "два" в обозначении указывает на то, что транзистор, осуществляющий питание (инжектор), работает в режиме двойной инжекции.

На рис. 10 изображен инвертор, выполненный в интегральной инжекционной логике. Питание  $\mathrm{U}^2\Pi$ -схем осуществляется от источника тока через p-n-p-переход транзисторов  $\mathrm{VT}_{\mathrm{II}}$ , имеющих общую эмиттерную p-область, называемую инжектором. Транзисторы  $\mathrm{VT}_{\mathrm{II}}$  имеют продольную структуру, причем p-область базы транзистора  $\mathrm{VT}_{\mathrm{II}}$  физически совмещена с эмиттерной p-областью транзистора  $\mathrm{VT}_{\mathrm{II}}$

Рис. 10

Изменение значений переменной x на входе изменяет путь тока инжекции  $I_{\Pi} = \alpha_u \cdot I$ . При x = 1, соответствующей высокому потенциалу на входе, ток  $I_{\Pi}$  поступает на базу транзистора VT, вызывая его насыщение. На выходе устанавливается низкий потенциал, соответст-вующий логическому "0": F = 0. При x = 0, что соответствует входному потенциалу, близкому к нулю, весь ток  $I_{\Pi}$  поступает во входную цепь. Транзистор VT закрывается, и

на выходе устанавливается высокий потенциал: F = 1.

#### Параметры логических элементов

Cредняя потребляемая мощность  $-P_{\rm cp}$ , определяемая как

$$P_{\rm cp} = 0.5 (P^0 + P^1),$$

где  $P^0$  — мощность, потребляемая логическим элементом, находящимся в состоянии "0",  $P^1$  — в состоянии "1". При возрастании частоты переключений элемента потребляемая мощность может существенно возрасти.

Koэффициент объединения по входу  $K_{ob}$  — определяет максимальное число входов логического элемента. Основные логические элементы имеют  $K_{ob} = 2 - 4$ . Увеличение числа входов достигается применением специального устройства — расширителя. При этом удается получить  $K_{ob} > 10$ .

$K_{\text{разв}}$ , определяет максимальное число аналогичных микросхем, которое можно подключить к данному логическому элементу без нарушения его нормальной работы. Выпускаемые промышленностью логические элементы имеют  $K_{\text{разв}} = 4 - 10$ . Увеличить нагрузочную способность можно, подключив к выходу логического элемента буферный усилитель.

*Быстродействие* — характеризуется временем задержки распространения сигнала и определяет быстроту реакции логического элемента при воздействии входного напряжения.

Помехоустойчивость – характеризует невосприимчивость логических элементов к изменению своих состояний под воздействием напряжения помех. Помехоустойчивость оценивается наибольшим напряжением помехи, которая не вызывает ложного срабатывания логического элемента.

В табл. 4 приведены основные параметры цифровых логических элементов различных типов.

| Параметр                             | ТТЛ     | ЭСЛ         | И²Л      | nМОП    | КМОП          |

|--------------------------------------|---------|-------------|----------|---------|---------------|

| Напряжение питания $E_{\rm K}$ , В   | 5       | -5,2        | 1,0      | 5       | 3–15          |

| Потребляемая мощность $P_{cp}$ , мВт | 2–44    | 35          | 0,01-0,1 | 0,1-1,5 | 0,01-0,1      |

| $K_{ m o f o}$                       | 2–8     | 2–5         | 1        | 2–5     | 2–5           |

| $K_{ m paз B}$                       | 10      | 15          | 5-10     | 100-200 | 100-200       |

| Быстродействие, нс                   | 5-20    | 0,7–3       | 10-20    | 20-200  | 50-100        |

| Генерация помех                      | Сильная | Отсутствует | Малая    | Малая   | Малая         |

| Уровень допусти-<br>мых помех        | 0,8     | 0,15        | 0,1      | 0,5     | $0,4E_{ m K}$ |

#### 4. ТРИГГЕРЫ

$\mathit{Триггером}$  называют устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое.

Триггеры являются базовыми элементами при построении счетчиков, регистров, дешифраторов и других устройств импульсной техники.

Характерной особенностью триггеров является способность сохранять двоичную информацию (состояние "0" или "1") после окончания действия входных импульсов. Это свойство обусловлено тем, что факторами, определяющими состояние триггера, являются не только внешние управляющие сигналы, но и внутренние сигналы самого триггера (сигналы обратной связи). Поэтому триггер может быть использован как элемент памяти, а совокупность триггеров может запомнить и хранить код некоторого числа.

В интегральной микросхемотехнике триггеры выполняют либо на основе логических интегральных элементов, либо как завершенный функциональный элемент в виде микросхемы.

Триггеры можно классифицировать по функциональному признаку и способу управления.

По функциональному признаку различают триггеры R, S, D, T, JK и других типов.

По способу управления различают асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информа-ционный вход. В тактируемых триггерах кроме информационных входов имеется вход тактовых импульсов. Переключение происходит только при наличии разрешающего, тактирующего импульса.

## **4.1.** *RS*-триггер

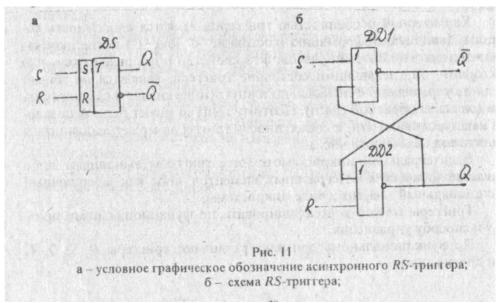

Асинхронный RS-триггер представляет собой устройство, кото-рое составляет основу всех остальных типов триггеров. Условное графическое обозначение RS-триггера на электрических схемах приведено на рис. 11, а. Название происходит от двух английских слов — "set—reset" ("устанавливать—сбрасывать"). Схема RS-триггера представляет собой два логических элемента ИЛИ — НЕ (И — НЕ), замкнутых в кольцо (рис. 11, б).

Схема имеет два входа: S и R, и два выхода: прямой Q и инверсный Q. В исходном состоянии (S=R=0) на выходе Q имеем логическую единицу, на выходе Q — нуль. При подаче сигнала на вход триггер должен устанавливаться в состояние логической единицы на входе Q и логического нуля на выходе Q. При подаче сигнала на вход R триггер устанавливается в исходное состояние: логический нуль — на выходе Q и логическая единица — на выходе Q.

Для RS-триггера комбинация на входе  $R=1,\,S=1$  является запрещенной.

Рис. 11 a — условное графическое обозначение асинхронного *RS*-триггера; б — схема *RS*-триггера;

Работа асинхронного *RS*-триггера однозначно описывается таб-лицей истинности (табл. 5).

Для RS-триггера на элементах И — НЕ входы R и S будут инверсные по сравнению со схемой рис. 11, б.

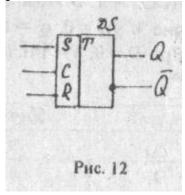

Cинхронный RS-триггер имеет три входа. Два из них логические: вход S является входом установки триггера в единицу, вход R является входом установки триггера в ноль (сброса). Третий вход C в синхронных системах служит для приема тактовых импульсов и не имеет ло- гического значения. Условное графическое обозначение синхронного RS-триггера приведено на рис. 12.

Таблица 5

| Так   | CT n  | Такт <i>n</i> +1 |

|-------|-------|------------------|

| $R^n$ | $S^n$ | $Q^{n+1}$        |

| 0     | 0     | 0                |

| 0     | 1     | 1                |

| 1     | 0     | 0                |

| 1     | 1     | Неопределенность |

## 4.2. *D*-триггер

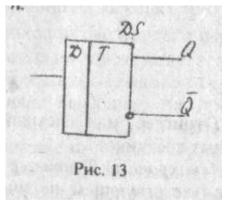

Для приема информации по одному входу используют D-триг-геры. На рис. 13 приведено условное графическое обозначение D-триг-гера. Из таблицы истинности D-триггера (табл. 6) следует, что логическое значение переменной в такте n+1 совпадает со значением вход-ной переменной в предшествующем такте n.

Таблица 6

| Такт п | Такт <i>n</i> +1 |

|--------|------------------|

| $D^n$  | $Q^{n+1}$        |

| 0      | 0                |

| 1      | 1                |

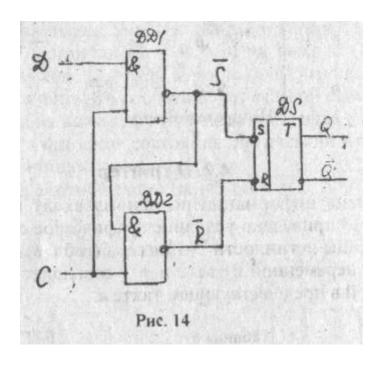

На рис. 14 приведена схема D-триггера на элементах И — НЕ. D-триггер переходит в состояние "1" (Q = 1), если в момент прихода синхронизирующего сигнала (C = 1) на его информационном входе сигнал "1". В этом состоянии триггер остается и после окончания сигнала на входе D до прихода очередного синхронизирующего сигнала, возвращающего триггер в состояние "0". Таким образом, Д-триггер "задерживает" поступившую информацию на время, равное периоду синхронизирующих сигналов.

Действительно, при D=1, C=1 на выходе  $\overline{S}$  элемента DD1 сигнал "0" (S=0), а на выходе DD2-"1"  $(\overline{R}=1)$ . Так как RS-триггер имеет инверсные входы, то при  $\overline{S}=0$ ,  $\overline{R}=1$  он переходит в состояние "1"  $(Q=1,\overline{Q}=0)$  и остается в этом состоянии до тех пор пока при D=0 не получится C=1. В этом случае  $\overline{S}=1$ ,  $\overline{R}=0$  и триггер возвращается в состояние "0"  $(Q=0,\overline{Q}=1)$ .

При D = 0, S = 1 и, не зависимо от C, Q = 0.

Рис. 14

## **4.3.** *Т*-триггер

T-триггер, или счетный триггер, используется для построения двоичных счетчиков.

$Aсинхронный \ T$ -триггер переходит в противоположное состояние при соответствующем логическом переходе на его T-входе. Условное графическое обозначение асинхронного триггера приведено на рис. 15, а.

Синхронный Т-триггер переходит в противоположное состояние при соответствующем логическом уровне на его входе и при наличии единицы на его синхронизирующем входе.

Рис. 15 а – условное графическое обозначение асинхронного *T*-триггера, б – схема асинхронного *T*-триггера

Функционирование T-триггера определяется табл. 7.

Таблица 7

Схема асинхронного T-тригге-ра приведена на рис. 15, б. Он состоит из RS-триггера и логических схем на его входах. Переход напряжения на входе T воздействует на две схемы И. Однако сигнал на выходе будет появляться только у той схемы И, на второй вход

| Такт п | Такт <i>n</i> +1 |

|--------|------------------|

| T      | $Q^{n+1}$        |

| 0      | $Q^n$            |

| 1      | $Q^n$            |

|        |                  |

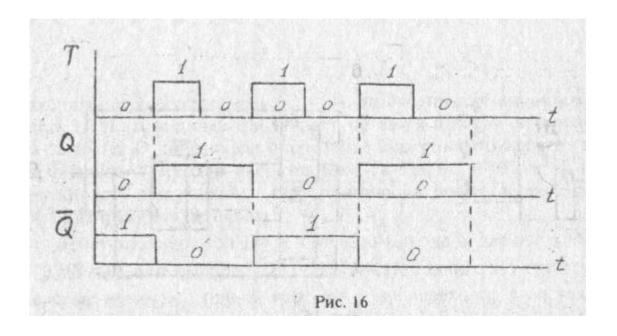

которой также подана логическая единица с выходов триггеров Q или Q. Так как только на одном из выходов RS-триггера может быть логическая единица, срабатывает одна из схем W, сигнал с которой поступит на один из входов RS-триггера и изменит его состояние. При этом изменятся логические уровни на выходах триггера Q и  $\overline{Q}$  и подключится другая схема W. С приходом следующего перепада напряжения на входе W эта схема W срабатывает и возвращает триггер в исходное состояние. Таким образом, с приходом каждого последующего сигнала на вход W-триггер изменяет состояние на противо-положное. Из временной диаграммы (рис. 16) следует, что частота выходных импульсов в два раза меньше частоты перепадов на входе W

Свойство деления частоты входных логических воздействий на два позволяет использовать T-триггер для построения двоичных счетчиков. При этом T-триггеры соединяются последовательно.

Рис. 16

## **4.4.** *JK*-триггер

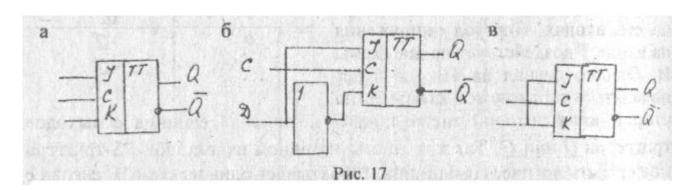

*JK*-триггеры являются универсальными и получили наибольшее распространение в системах интегральных логических элементов. Универсальность их заключается в том, что путем частичных изменений при переключении входов можно получить другие типы триггеров.

Условное графическое обозначение JK-триггера приведено на рис. 17, а.

Рис. 17 а — условное обозначение *JK*-триггера; б — схема *D*-триггера на основе *JK*-триггера; в — схема *T*-триггера на основе *JK*-триггера.

Триггер этого типа является усовершенствованным вариантом двухвходного триггера. Как видно из табл. 8, в отличие от RS-триггера состояние J=1, K=1 является допустимым.

|    |        | Таблица 8 |

|----|--------|-----------|

| Та | Такт п |           |

| J  | K      | $Q^{n+1}$ |

| 0  | 0      | $Q^n$     |

| 0  | 1      | 0         |

| 1  | 0      | 1         |

| 1  | 1      | $Q^n$     |

Используя вход J как вход S, а K как R, реализуют синхронный RS-триг-гер, особенность которого состоит в том что при комбинации S=R=1, запрещенной для обычного JK-триггера, он переключается на каждый синхронизирующий сигнал. Добавлением инвертора на входе JK-триггера получают D-триг-гер (рис. 17, б). Соединяя входы JK-триггера по схеме на рис. 17, в

получают T-триггер.

## 5. ЦИФРОВЫЕ СЧЕТЧИКИ ИМПУЛЬСОВ

В устройствах цифровой обработки информации измеряемый параметр (угол поворота, перемещение, скорость, частота и т. д.) преобразуется в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра.

Цифровым счетчиком импульсов называют устройство, реализующее счет числа входных импульсов и фиксирующее это число в каком-либо коде.

Интерес к таким устройствам объясняется их высокой точностью, а также возможностью осуществления связи с ЭВМ.

В зависимости от способа реализации счета счетчики подразделяются на суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные. В суммирующем счетчике при поступлении каждого входного сигнала код увеличивается на единицу, а в вычитающем — уменьшается. Реверсивный счетчик может работать как в режиме сложения, так и в режиме вычитания.

Основными характеристиками счетчика являются быстродействие и модуль счета, или коэффициент пересчета  $K_{\rm cч}=2^n$ , где n — разрядность счетчика или количество содержащихся в нем триггеров.

Модуль счета характеризует число устойчивых состояний счетчи-ка, т. е. максимальное число входных сигналов, которое может быть со-считано счетчиком. Например, в четырехразрядном счетчике  $K_{\rm cч}=2^4==16$ , счетчик будет иметь 16 устойчивых состояний. При этом каждый 16-й входной сигнал устанавливает счетчик в исходное состояние.

Наибольшее распространение получили счетчики на T- и JK- триггерах. Рассмотрим простейшую схему двоичного суммирующего счетчика

## с непосредственной связью.

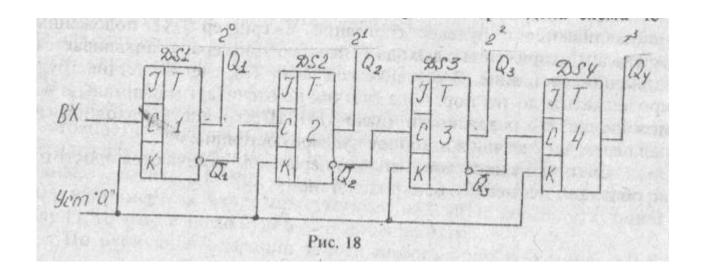

Рис. 18

На рис. 18 приведена схема четырехразрядного счетчика, построенного на *JK*-триггерах. Основным узлом двоичного счетчика является триггер со счетным запуском. Счетные импульсы подаются на вход первого триггера. Счетные входы поступающих триггеров непосредственно связаны с инверсными выходами предыдущих.

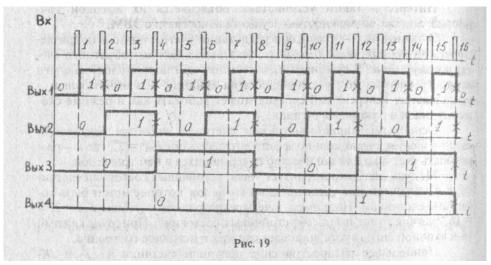

Работу схемы иллюстрируют временные диаграммы на рис. 19. Перед поступлением счетных импульсов все разряды счетчика устанавливаются в состояние "0" ( $Q_1 = Q_2 = Q_3 = Q_4 = 0$ ) подачей сигнала "Ус-тановка 0". В счетчике устанавливается код 0000.

При поступлении на вход первого импульса триггер DS1 уста- навливается в единичное состояние. В счетчике устанавливается код 0001.

Рис. 19

При поступлении второго входного импульса первый триггер устанавливается в нулевое состояние, а триггер DS2 положенным перепадом напряжения с выхода Q первого триггера устанавливается в единичное состояние. В счетчике код 0010. Так счет в счетчике будет продолжаться до тех пор, пока счетчик не отсчитает максимально возможное для его разрядности число 1111. Шестнадцатый входной сигнал переведет счетчик в исходное нулевое состояние.

Счетчики с последовательным переносом отличаются простотой, но обладают невысоким быстродействием.

#### 6. РЕГИСТРЫ

Регистрами называются функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации. Регистры являются наиболее распространенным типом последовательных узлов в современных ЭВМ. Иногда в регистре предусматривается возможность сдвига числа на один или несколько разрядов в сторону младших или старших разрядов. Такие регистры называются сдвигающими, они используются при выполнении арифметических операций. В зависимости от способа ввода и вывода разрядов числа различают регистры параллельные, последовательные и параллельно-последовательные. Ввод, вывод, сдвиг и другие операции осуществляются управляющими сигналами, которые поступают в регистр по специальным управляющим шинам (проводам).

## 6.1. Параллельные регистры

В параллельных регистрах запись двоичного числа осуществля-ется параллельным кодом, т. е. во все разряды регистра одновременно. Их функции сводятся к приему, хранению и передаче информации (двоичного числа). В связи с этим параллельные регистры часто называют регистрами памяти.

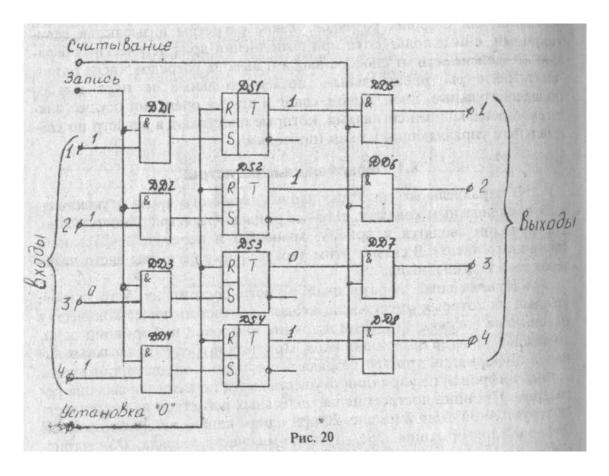

Параллельный *N*-разрядный регистр состоит из *N*-триггеров, каждый из которых имеет число входов, соответствующее количеству источников информации. Если источник цифровой информации один, то каждый триггер имеет один вход. При двух и трех параллельных каналах информации триггер разряда выполняется на два и три входа. Запись цифровой информации осуществляется по цепи управления регистром. Принцип построения параллельных регистров иллюстрируется структурной схемой на рис. 20 при

одном канале четырехразрядной цифровой информации. DS1 — триггер младшего разряда, DS4 — триггер старшего разряда; DD1—DD4 — логические элементы, предназначенные для управления записью информации в регистр; DD5—DD8 — элементы, служащие для управления считыванием информации из регистра.

Перед записью двоичного числа все триггеры устанавливают в состояние "0" подачей импульса по входу "Установка 0". Для записи в регистр входной информации подают импульс записи, открывающий входные элементы И. Код входного числа записывается в регистр. Если, например, на входе присутствует код 1011, соответствующий числу 11, то это же число будет записано в регистр.

По окончании операции записи информация, записанная в регистр сохраняется, несмотря на то что входная информация (число) может изменяться.

Для считывания информации подают импульс по входу "Считывание". На выходные шины регистра передается код числа, записанного в регистр. При этом число, записанное в регистр, сохраняется. Для получения новой информации описанные операции повторяются.

Рис. 20

## 6.2. Последовательные регистры

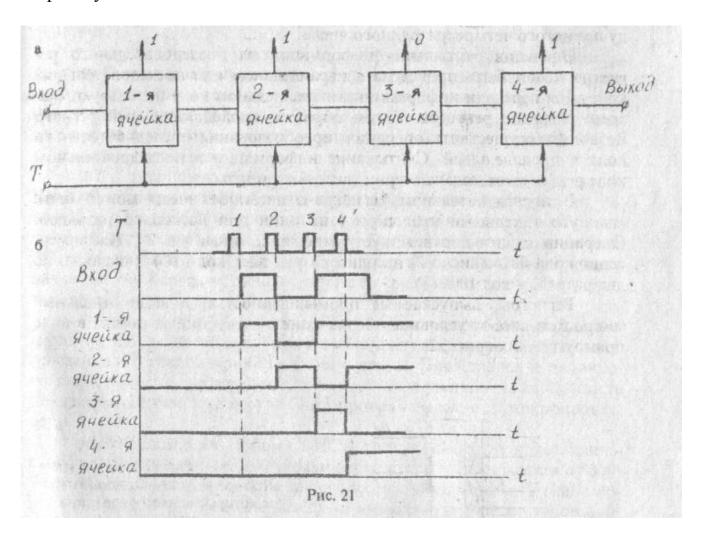

Последовательные регистры (регистры сдвига) характеризуются записью числа последовательным кодом. Регистр состоит из последовательно соединенных двоичных ячеек памяти, состояние которых передается (сдвигается) на последующие ячейки под действием тактовых импульсов. Тактовые импульсы управляют работой регистра. Управление может осуществляться одной последовательностью тактовых импульсов. В этом случае регистры называют однотактными.

Частота следования тактовых импульсов обычно неизменна. На рис. 21, а показана структурная схема сдвигающего регистра для четырех разрядов. Первая ячейка регистра относится к младшему разряду, а четвертая – к старшему.

Рис. 21

При таком расположении разрядов запись числа в регистр производится, начиная с его старшего разряда. При обратном расположении разрядов в регистре запись числа должна начинаться с младшего разряда.

Тактовые импульсы подаются на все триггеры ячеек одновременно. Их воздействие направлено на переключение триггеров из состояния "1" в состояние "0" с записью единицы в триггер следующей ячейки. На рис. 21, б приведены временные диаграммы, поясняющие процесс записи информации в регистр. В качестве примера взят код 1011, соответствующий числу 11. Перед записью информации регистр устанавливают в состояние "0". Для этого в отсутствие сигнала на входе подается серия тактовых импульсов с числом импульсов, равным количеству разрядов в регистре. При записи информации одновременно с поступлением кода числа подаются тактовые импульсы. Тактовыми импульсами осуществляется продвижение информации от младшего разряда регистра к старшему. В результате после четвертого тактового импульса ячейки регистра принимают состояния, соответствующие коду принятого четырехразрядного числа.

Операция считывания информации из последовательного регистра может быть проведена в параллельном или последовательном коде. Для передачи информации в параллельном коде используют выходы разрядов регистра. Таким образом, последовательный регистр позволяет осуществить операцию преобразования последовательного кода в параллельный. Считывание информации в последовательном коде реализуется подачей серии тактовых импульсов.

В последовательном регистре записанное число может быть сдвинуто тактовыми импульсами на один или несколько разрядов. Операции сдвига соответствует умножение числа на  $2^{K}$ . Например, сдвиг кода 0010 (число 2) на один разряд дает код 0100 (число 4), на два разряда — код 1000 (8).

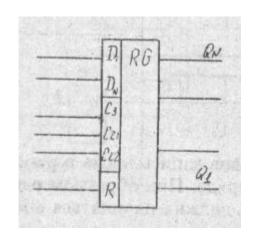

Регистры, выпускаемые промышленностью в виде отдельных микросхем, имеют условное обозначение в электронных схемах в виде прямоугольника рис. 22.

Рис. 22

RG — регистр;  $D_1$ — $D_n$  — входы, на которые подается код числа для записи;  $C_3$  — вход команды записи;  $C_{\rm ч1}$ ,  $C_{\rm ч2}$  — входы для команды считывания; R — установка регистра в нулевое положение;  $Q_1$ ,  $Q_n$  — выходы

### 7. МИКРОПРОЦЕССОРЫ

Микропроцессором (МП) называют программно управляемое микроэлектронное устройство, осуществляющее обработку цифровой информации. Микропроцессор содержит одну или несколько больших интегральных схем. В случае использования нескольких больших интегральных схем, они должны быть совместимы, т. е. предназначены для совместного применения с общими источниками питания, иметь единую систему логических сигналов, одинаковую разрядность и быстродействие.

Микропроцессор реализует такие функции, как выборку в предписанной программной последовательности, декодирование и управление выполнением команд, а также выполнение операций тестирования и преобразования данных. Таким образом, он осуществляет заданную в виде программы последовательность действий – процесс, откуда и название – процессор.

МП оперирует информацией в двоичной системе счисления. Каждый разряд двоичного числа называется *битом*. Информация, которую обрабатывает микропроцессор, представляется группой битов, которые составляют *слово*. Количество битов в слове зависит от типа МП и может быть 4, 8, 12, 16 и т. д. Количество битов в слове, предназначенное для передачи данных, равно числу проводников и образует так называемую шину данных.

Группа, состоящая из восьми битов называется *байтом*. Деление слова на байты позволяет упростить представление двоичного кода, применив шестнадцатиричную форму записи. Представление двоичного слова в шестнадцатиричном коде позволяет уменьшить вероятность появления ошибок

при составлении программы работы микропроцессора.

МП представляет собой СБИС — тонкую пластину кристаллического кремния в форме прямоугольника со сторонами размером от 3 до 7 мм. Пластина монтируется в пластмассовый или металлический корпус шириной  $10{\text -}15$  мм и длиной  $20{\text -}70$  мм. Вдоль длинных сторон корпуса располагаются выводы в количестве  $16{\text -}60$  для соединения МП — с другими устройствами. Первый МП появился в 1971 г. и содержал 2250 транзисторов из четырех кристаллов, с кристаллом ОЗУ емкостью 32 бита. Уже в 1974 г. был разработан МП К580, содержащий 5 тыс. транзисторов с памятью 64 Кбайта (1 Кбайт =  $1024 = 2^{10}$ ), а в 1984 г. был разработан МП типа К1810, содержащий 29 тыс. транзисторов с памятью в 1 Мбайт ( $2^{20}$ ).

Применение микропроцессорных модулей: 80% МП входят в состав автоматизированных систем управления, а 20% — используются для построения ЭВМ. По прогнозам к 2000 г. число выпускаемых МП превысит число электрических ламп и составит 5–10 млрд штук.

Упрощенная структурная схема микропроцессора серии К580 МК 80 А представлена на рис. 23.

Рис. 23

МП состоит из схем, реализующих арифметические и логические операции над данными различных регистров, служащих для временного хранения и преобразования данных и команд, а также устройств управления и связи с внешними блоками.

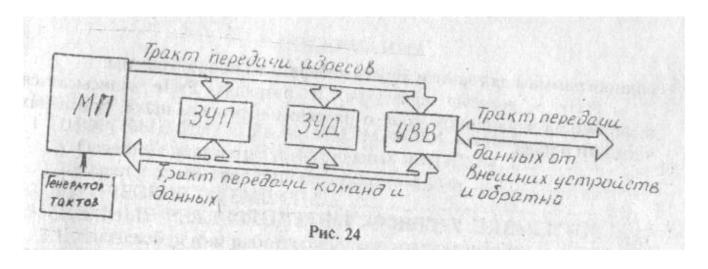

МП применяют совместно с запоминающим устройством программы (ЗУП), с запоминающим устройством данных (ЗУД), а также с устройством ввода-вывода (УВВ).

Система, состоящая из микропроцессора и указанных устройств, получила название микропроцессорной системы, или микроЭВМ (рис. 24).

Рис. 24

Функционирование всех узлов и блоков микропроцессорной системы осуществляется с помощью генератора тактовых импульсов.

$Pezucmp\ команд$   $P_p$ К предназначен для хранения в МП команды, считанной из ЗУП, на период ее выполнения. Выполнение команды осуществляется блоком управления БУ, который связан с общими регистрами МП.

Аккумулятор АК представляет собой основной регистр, предназначенный для ввода данных в МП и вывода их из него. В аккумулятор поступает операнд (числа) из ЗУД перед проведением соответствующей операции в арифметико-логическом устройстве. В аккумулятор же вводится результат проведенной в АЛУ операции.

Арифметическо-логическое устройство АЛУ осуществляет операции сложения, вычитания, сравнения, а также операции И, ИЛИ над двумя числами (операндами) с выдачей результата по одному выходу. Вид операции задается командным кодом, содержащимся в регистре команд.

Регистр временного хранения  $P_PBX_P$  предназначен для хранения данных перед проведением операций в АЛУ. Если, например, требуется провес-

ти операцию арифметического сложения двух чисел, то одно число предварительно хранится в аккумуляторе, а второе – в одном из регистров временного хранения.

Счетчик команд СК содержит адрес команды выбираемой  $P_p$ К из ЗУП в текущий момент времени. Он представляет собой суммиру-ющий счетчик, содержание которого увеличивается на единицу к концу выполнения текущей команды.

Если МП работает с подпрограммами, то в СК записывается предварительное число, соответствующее адресу первой команды подпрограммы, а по завершении последней команды в подпрограмме счетчик устанавливается на адрес команды основной программы.

Стековый регистр CP — производит операции записи и извлечения чисел. Содержимое SP автоматически уменьшается на 2 после каждой записи и увеличивается на 2 после каждого извлечения. Необходимость работы стекового регистра возникает при обращении к подпрограммам для записи адреса возврата из подпрограммы.

$P_{P}\Pi_{P}$  – регистр признаков. В разрядах  $P_{P}\Pi_{P}$  записывается информация в двоичном коде о разрядах переноса, знака, признаках четности и нуля.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. **Алексеенко А.**  $\Gamma$ . Основы микросхемотехники. Элементы морфологии микроэлектронной аппаратуры. 2-е изд., перераб. и доп. М.: Сов. радио, 1977. 405 с.

- 2. **Алексеенко А. Г.** Современная микросхемотехника. М.: Энергия. 1979. 112 с.

- 3. **Барков В. А.** Электроника робототехнических систем. Усилительно-преобразовательные устройства: Учеб. пособие. СПб.: СПбГТУ, 1993. 144 с.

- 4. **Забродин Ю. С.** Промышленная электроника. М.: Высш. шк., 1982. 496 с.

- 5. Основы промышленной электроники: Учеб. для неэлектротехнических спец. вузов / В. Г. Герасимов, О. М. Князьков, А. Е. Крас- нопольский, В. В. Сухоруков / Под ред. В. Г. Герасимова. М.: Высш. шк., 1986. 336 с.

- 6. Основы радиоэлектроники: Учеб. пособие / Ю. П. Волощенко, Ю. Ю. Мартюшев, И. Н. Никитина и др. Под ред. Г. Д. Петрухина. М.: Изд-во МАИ, 1993. 416 с.

- 7. **Фишер Дж., Гетланд Х. Б**. Электроника от теории к практике: Пер. с англ. М.: Энергия, 1980. 400 с.

- 8. **Хоровиц П., Хилл У.** Искусство схемотехники: В 3 т.: Пер. с англ. М.: Энергия, 1980. 400 с.

- 9. Цифровые и аналоговые микросхемы: Справ. / С. В. Якубов-ский, Л. И. Ниссельсон, В. И. Кулешова и др. М.: Радио и связь, 1990. 496 с.

- 10. Электротехнический справочник: В 3 т. Т. 2. Электротехниче-ские изделия и устройства. М.: Энергоатомиздат, 1986. 712 с.

# СОДЕРЖАНИЕ

| ВВЕДЕНИЕ                                                | 3  |

|---------------------------------------------------------|----|

| 1. ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ                     | 4  |

| 1.1. Основные параметры интегральных микросхем          | 6  |

| 1.2. Серии и семейства серий интегральных схем          | 7  |

| 2. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ                                  | 7  |

| 3. СХЕМНЫЕ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ              | 11 |

| 3.1. Ключевой режим работы биполярного транзистора      | 12 |

| 3.2. Транзисторно-транзисторная логика (ТТЛ)            | 14 |

| 3.3. Логические элементы на основе полевых транзисторов | 15 |

| 3.3.1. МОП-транзисторная логика на ключах одного типа   |    |

| проводимости                                            | 15 |

| 3.3.2. МОП-транзисторная логика на комплиментарных      |    |

| транзисторах (КМОП-логика)                              | 16 |

| 3.4. Эмиттерно-связанная логика (ЭСЛ)                   |    |

| 3.5. Интегральная инжекционная логика ( $H^2$ Л-логика) | 19 |

| Параметры логических элементов                          | 20 |

| 4. ТРИГГЕРЫ                                             | 21 |

| 4.1. <i>RS</i> -триггер                                 | 22 |

| 4.2. <i>D</i> -триггер                                  | 23 |

| 4.3. <i>Т</i> -триггер                                  | 25 |

| 4.4. <i>JK</i> -триггер                                 | 27 |

| 5. ЦИФРОВЫЕ СЧЕТЧИКИ ИМПУЛЬСОВ                          | 28 |

| 6. РЕГИСТРЫ                                             | 30 |

| 6.1. Параллельные регистры                              | 30 |

| 6.2. Последовательные регистры                          | 32 |

| 7. МИКРОПРОЦЕССОРЫ                                      |    |

| СПИСОК ЛИТЕРАТУРЫ                                       | 38 |

$3 \quad 4 \qquad nMO\Pi$

$E_{

m K}$   $E_{

m K}$   $I_{

m C}$

$E_{\mathrm{K}}$   $E_{\mathrm{K}}$   $I_{\mathrm{C}}$

SP

приборов (например, от устройств для измерения температуры, дав- ления, влажности). Пример аналогового сигнала  $U\left(t\right)$  приведен на рис. 1, а.

#### Евстигнеев Анатолий Николаевич

## Кузьмина Татьяна Георгиевна Новотельнова Анна Владимировна

#### ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

Методические указания для самостоятельного изучения дисциплины "Электротехника и основы электроники" для студентов всех специальностей

Редактор М. Б. Кановская

Корректор Н. И. Михайлова

ЛР № 020414 от 12. 02. 97 Подписано в печать 16.11. 99. Формат 60×84 1/16. Бум. газетная Печать офсетная Усл. печ. л. 2,09. Печ. л. 2,25. Уч.-изд. л. 2,19 Тираж 500 экз. Заказ № С 7

СПбГАХПТ. 191002, Санкт-Петербург, ул. Ломоносова, 9 ИПЦ СПбГАХПТ. 191002, Санкт-Петербург, ул. Ломоносова, 9