А.Л. Андреев, В.В. Коротаев

# ЭЛЕМЕНТЫ И УЗЛЫ ЭЛЕКТРОННЫХ И ОПТИКО-ЭЛЕКТРОННЫХ ПРИБОРОВ

Учебное пособие

## МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ УНИВЕРСИТЕТ ИТМО

## А.Л. Андреев, В.В. Коротаев

## ЭЛЕМЕНТЫ И УЗЛЫ ЭЛЕКТРОННЫХ И ОПТИКО-ЭЛЕКТРОННЫХ ПРИБОРОВ

### УЧЕБНОЕ ПОСОБИЕ

Санкт-Петербург 2015 Андреев А.Л., Коротаев В.В. Элементы и узлы электронных и оптико-электронных приборов, Учебное пособие. – СПб: Университет ИТМО, 2015. – 150 с.

Рассматриваются базовые элементы и узлы, которые могут входить в структуру функциональных модулей предпроцессорной обработки аналоговых и бинарных сигналов, а также модулей управления различными исполнительными устройствами ОЭС. Приводятся различные примеры типовых модулей обработки, преобразования и сопряжения сигналов, которые могут применяться в структуре аппаратных средств ОЭС различного назначения.

Учебное пособие предназначено для студентов, обучающихся по направлению подготовки бакалавров 12.03.02 «Оптотехника» и специальности 12.05.01 «Электронные и оптико-электронные приборы и системы специального назначения».

Рекомендовано Учебно-методическим объединением вузов Российской Федерации по образованию в области приборостроения и оптотехники для студентов высших учебных заведений, обучающихся по направлению подготовки бакалавров 12.03.02 «Оптотехника» и специальности 12.05.01 «Электронные и оптико-электронные приборы и системы специального назначения» протокол №5 от 01.09.2015.

## университет итмо

ведущий Университет ИТМО – BV3 России области информационных и фотонных технологий, один из немногих российских вузов, получивших в 2009 году статус национального исследовательского университета. С 2013 года Университет ИТМО – участник программы повышения конкурентоспособности российских университетов среди мировых научно-образовательных центров, ведущих известной как Университета проект «5 100». Цель ИТМО – становение исследовательского университета мирового уровня, предпринимательского по типу, ориентированного на интернационализацию всех направлений деятельности.

> © Университет ИТМО, 2015 ©Андреев А.Л. Коротаев В.В., 2015

#### Содержание

| Введение                                                        | 4   |

|-----------------------------------------------------------------|-----|

| 1 Базовые элементы обработки аналоговых сигналов                | 5   |

| 1.1 Операционные усилители. Общие определения, параметры        | И   |

| характеристики                                                  | 5   |

| 1.2 Типовые схемы включения операционного усилителя             |     |

| 1.3 Электронные ключи и коммутаторы аналоговых сигналов         |     |

| 1.4 Фотоприёмный узел на основе пары фотодиод – операционн      |     |

| усилитель                                                       |     |

| 1.5 Координатно-чувствительный фотоприёмный узел на осн         |     |

| четырёхэлементного фотодиода                                    |     |

| 2 Базовые элементы и узлы обработки бинарных сигналов           |     |

| 2.1 Базовые логические элементы наиболее распространённых сер   | _   |

| цифровых интегральных схем и эксплуатационных параметр          |     |

| предопределяющих выбор элементной базы                          |     |

| 2.3 Комбинационные логические схемы                             |     |

| 2.4 Последовательные логические схемы                           |     |

| 2.5 Программируемые логические интегральные схемы (ПЛИС)        |     |

| 2.6 Устройства сопряжения узлов обработки аналоговых и бинарн   | ных |

| сигналов в составе аппаратных средств ОЭС                       |     |

| 3 Типовые модули обработки, преобразования и сопряжения сигнало | В В |

| структуре аппаратных средств ОЭС                                | 87  |

| 3.1 Управление светодиодами                                     | 87  |

| 3.2 Управление электромагнитными реле                           |     |

| 3.3 Управление шаговыми двигателями                             |     |

| 3.4 Оптроны и их применение в функциональных модулях электронн  |     |

| гракта ОЭП                                                      |     |

| 3.5 Фиксаторы уровня и пиковые детекторы                        |     |

| 3.6 Устройство выборки-хранения                                 |     |

| 3.7 Модуль предварительной обработки видеосигнала               |     |

| вычислительными устройствами                                    |     |

| 4 Пример использования некоторых модулей предварительной обрабо |     |

| сигналов в структуре оптического локатора                       |     |

| Заключение                                                      |     |

| Литература                                                      |     |

| JIVITEDATVDA                                                    | 142 |

#### Введение

Процесс проектирования современных оптико-электронных систем (ОЭС) обычно включает решение комплекса задач, связанных с разработкой аппаратных средств и соответствующего программного обеспечения. Возможные алгоритмы цифровой обработки сигналов, методы их моделирования и реализации с помощью встраиваемых или сопрягаемых вычислительных устройств рассматриваются в других учебных пособиях (смотри, например, [1, 2]). Настоящее пособие посвящено вопросам реализации функциональных модулей электронного тракта ОЭС, обеспечивающих первичное формирование, а также преобразование аналоговых и цифровых электрических сигналов, подлежащих дальнейшей обработке с помощью цифрового вычислительного устройства.

В первом и втором разделах рассматриваются базовые элементы и узлы, которые могут входить в структуру функциональных модулей предпроцессорной обработки аналоговых и бинарных сигналов, а также модулей управления различными исполнительными устройствами ОЭС.

В третьем разделе приводятся различные примеры наиболее типовых модулей обработки, преобразования и сопряжения сигналов, которые могут применяться в структуре аппаратных средств ОЭС различного назначения.

Четвёртый раздел иллюстрирует пример аппаратной реализации одного из эффективных алгоритмов фильтрации помех на основе использования специализированных модулей предварительной (предпроцессорной) обработки сигналов в структуре оптического локатора.

Материал **учебного** пособия базируется следующих предшествующих дисциплинах: «Общая электроника», «Электроника и микропроцессорная техника», «Источники и приёмники оптического излучения». С целью облегчения восприятия рассматриваемых вопросов и усвоения материала авторы также рекомендуют глубокого обращаться к дополнительным изданиям (смотри, например, [3, 4, 5, 6, 7]), в которых более подробно излагаются общие основы электроники и работы полупроводниковых приборов, составляющих структуру современной элементной базы аппаратных средств ОЭС.

#### 1 Базовые элементы обработки аналоговых сигналов

## 1.1 Операционные усилители. Общие определения, параметры и характеристики.

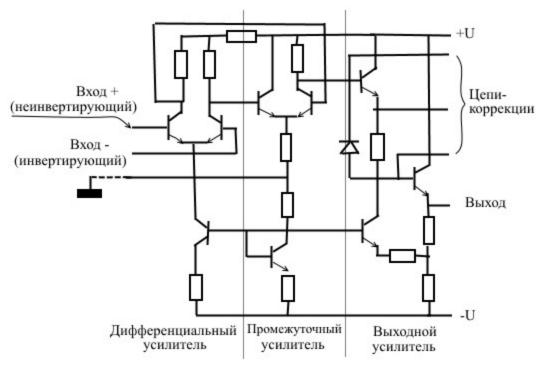

Операционный усилитель (ОУ) — универсальный электронный прибор, предназначенный для выполнения различных операций над аналоговыми сигналами. ОУ по существу представляет собой усилитель постоянного тока (УПТ) с дифференциальным входом. На рис. 1.1 в качестве примера приведена принципиальная электрическая схема одного из отечественных ОУ К140УД1.

Рисунок 1.1- Принципиальная электрическая схема ОУ К140УД1

ОУ обладает очень большим коэффициентом усиления  $K_0$ , очень малыми входными токами  $I_{\rm Bx}$ , очень большим входным сопротивлением  $R_{\rm Bix}$ , очень большой граничной частотой усиления  $f_{\rm rp}$ , а также очень малым смещением нуля  $U_{\rm cm}$ . Здесь под очень большими и очень малыми следует понимать такие величины, которые в простых расчетах можно считать соответственно бесконечными или нулевыми, вводя, таким образом, понятие идеального операционного усилителя.

Итак, будем полагать, что у идеального ОУ

$$K_0 = \infty$$

;  $f_{\text{rp}} = \infty$ ;  $f_{\text{rp}} = \infty$ ;  $I_{\text{вы}} = 0$ ;  $U_{\text{см}} = 0$ . (1.1)

В зависимости от параметров цепи обратной связи (заметим, что без обратной связи ОУ практически не используются) на базе ОУ возможно

построение схем с нужной передаточной функцией. Таким образом, можно реализовывать прецизионные масштабирующие усилители, генераторы функций, стабилизаторы напряжения или тока, активные фильтры, логарифмирующие и потенцирующие усилители, аналоговые интеграторы и дифференциаторы и т.д. Можно насчитать сотни других стандартных схем различных функциональных узлов, которые можно синтезировать на ОУ.

Операционные усилители обычно питаются от симметричных источников, обеспечивающих одинаковые по величине положительное и отрицательное напряжение  $+U_{\rm II}$ ,  $-U_{\rm II}$  относительно общего (нулевого) провода, так называемой «земли». Для большинства современных ОУ напряжение питания можно менять в достаточно широких пределах от  $\pm$  3 В до  $\pm$  18 В. В военном исполнении диапазон напряжение питания ОУ расширен до  $\pm$  22 В.

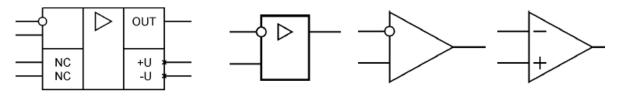

На рис. 1.2 а приведено условно-графическое обозначение ОУ, которое в соответствии с действующим ГОСТом следует использовать в конструкторской документации (NC — входы для дополнительной коррекции нуля). Однако в книгах, статьях и других изданиях допускается упрощённое обозначение ОУ (рис. 1.2б), на котором отсутствуют выводы для подключения питания и цепей коррекции. Кроме того в журнальных статьях, в интернет ресурсах, в неофициальных публикациях справочного характера, а также в изданиях зарубежных авторов можно встретить графическое обозначение ОУ, показанное на рис. 1.2 в,г.

Рисунок 1.2 – Условно-графические обозначения ОУ

Выходное напряжение связано с входным дифференциальным сигналом простым выражением, которое, по существу является основным уравнением ОУ

$$U_{\text{BMX}} = K_0 (U_{\text{BX}^+} - U_{\text{BX}^-}). \tag{1.2}$$

Здесь  $K_0$  — собственный коэффициент усиления ОУ без обратной связи в области низких частот ( $f << f_{\rm rp}$ .). Это один из основных параметров реального операционного усилителя. Величина  $K_0$  для разных типов ОУ изменяется в диапазоне  $10^4 \dots 10^7$ . Однако, разумеется, в любом случае выходное напряжение по абсолютной величине не может превышать напряжение питания  $|U_{\rm вых}| < |U_{\rm п}|$ .

Вследствие большого коэффициента усиления ОУ является высокочувствительным звеном электронного тракта, усиливающим как малые полезные сигналы, так и собственные шумы, а также внешние наводки и другие возможные помехи. При этом даже незначительная

асимметрия внутренних цепей и нестабильность параметров приводит к тому, что без отрицательной обратной связи ОУ просто непригоден для работы в линейном режиме, поскольку напряжение  $U_{\text{вых}}$  под влиянием шумов, и даже незначительных наводок, температурных уходов может принимать значения, близкие к напряжению источников питания (режим насыщения выходного каскада). Но при наличии глубокой отрицательно обратной связи (ООС) именно благодаря большому собственному коэффициенту усиления  $K_0$  удаётся добиться высокой стабильности параметров функциональных узлов на базе ОУ.

Ниже рассмотрим другие важные параметры и характеристики реальных операционных усилителей, во многом предопределяющие возможности их практического применения в структуре аппаратных средств электронного тракта оптико-электронных приборов.

Входное сопротивление ( $R_{\rm Bx}$ ) определяется как отношение  $\Delta U_{\rm Bx}/\Delta I_{\rm Bx}$  при заданной частоте сигнала. Фактически это сопротивление между входами ОУ. Необходимо помнить, что входное сопротивление ОУ и входное сопротивление схемы – это два разных понятия, величина их может отличаться на несколько порядков. Типовые значения  $R_{\rm Bx}$  на низких частотах для ОУ на биполярных транзисторах –  $10^4$  ...  $10^8$  Ом, для полевых –  $10^7$  ...  $10^{12}$  Ом.

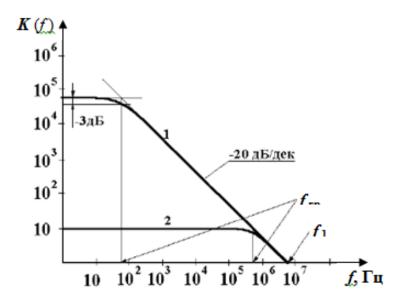

*Частота единичного усиления*  $(f_1)$  - это частота, на которой  $|K_0(f_1)| = 1$ . Характерная зависимость коэффициента усиления от частоты приведена на рис. 1.3.

Граничная частота ( $f_{\rm rp}$ ) определяется как частота, на которой коэффициент усиления уменьшается на 3 децибела:  $|K_0(f_1)| = 0.707 \times |K_0(0)|$  (график 1 на рис. 1.3). Область частот 0 ...  $f_{\rm rp}$  называют полосой пропускания. Введение ООС приводит к уменьшению коэффициента передачи (коэффициента усиления) функционального узла на ОУ, но при этом расширяет его полосу пропускания (смотри, например график 2 на рис. 1.3). Для формирования необходимой частотной характеристики вводят специальные частотно-зависимые корректирующие цепи, которые снижают коэффициент усиления на высоких частотах, приближая характеристику ОУ к звену первого порядка. Частотная коррекция может быть как внутренняя (140УД7, 544УД1), так и внешняя (553УД2, 140УД5). Такая частотная коррекция необходима для предотвращает самовозбуждение схемы.

Входной ток смещения ( $I_{\rm BX}$ ) это ток, протекающий во входную цепь ОУ. Он необходим для нормальной работы входных биполярных транзисторов. Для ОУ на полевых транзисторах это ток утечки затвора. Под  $I_{\rm BX}$  подразумевают среднее арифметическое двух токов  $I_{\rm BX}$  и  $I_{\rm BX}$ . У разных типов ОУ входной ток смещения изменяется в широких пределах. Так у ОУ на биполярных транзисторах  $I_{\rm BX}\approx 10^{-5}\dots 10^{-8}{\rm A}$ , у ОУ на полевых транзисторах  $I_{\rm BX}\approx 10^{-9}\dots 10^{-12}{\rm A}$ .

Рисунок 1.3 – Зависимость коэффициента усиления от частоты

Выходное сопротивление  $(R_{\rm вых})$  — внутреннее выходное сопротивление ОУ, которое можно определить как отношение  $U_{\rm xx}/I_{\rm K3}$  (напряжение холостого хода/ток короткого замыкания), и составляет для разных ОУ величину от нескольких десятков до нескольких сотен Ом. Типовое значение  $R_{\rm выx}$  для ОУ широкого применения 100 ... 1000 Ом.

Разность входных токов (ток сдвига)  $\Delta I_{\rm BX} = |I_{\rm BX} - I_{\rm BX}|$  определяется при заданном значении входного напряжения.  $\Delta I_{\rm BX}$  вызывает на выходе ОУ некоторое смещение (приведенное ко входу оно составляет величину 1...5 мВ и зависит от величины резисторов, подключаемых ко входам).

Напряжение смещения ( $U_{\rm cm}$ ) определяется как разность напряжений на входах, при котором  $U_{\rm вых}$ =0 при оговоренных сопротивлениях резисторов, подключаемых ко входам. Если значения этих резисторов стремятся к нулю, то напряжение смещения называют э.д.с. смещения ( $E_{\rm cm}$ ). Для ОУ с биполярными транзисторами на входе  $U_{\rm cm}$  составляет 1...10 мВ. Для ОУ с полевыми транзисторами на входе  $U_{\rm cm}$  обычно в несколько раз больше (до 30 мВ).

Таким образом, если на оба входа ОУ, не охваченного отрицательной обратной связью, подать точно равные напряжения, (например, оба входа заземлить), на выходе, скорее всего, будет наблюдаться уровень, близкий к одному из питающих напряжений (то есть ОУ войдет в режим ограничения). Так, например, при  $U_{\rm cm} \approx 10$  мВ и  $K_0 \approx 10^5 \ |U_{\rm Bыx}| = |U_{\rm cm}| \times K_0 \approx 10^{-2} \times 10^5 = 1000 \, {\rm B}$ , что значительно больше  $|U_{\rm n}|$ . Для того чтобы при подаче равного напряжения на оба входа усилителя выходное напряжение было близко к нулю, ОУ необходимо сбалансировать. Поэтому некоторые ОУ имеют специальные входы (входы NC – коррекция нуля, рис. 1.2 а).

Средний температурный дрейф напряжения смещения ( $\Delta U_{\rm cm}/\Delta T$ ) — максимальное изменение  $U_{\rm cm}$  при изменении температуры на 1°C в ого-

воренном диапазоне температур. Измеряется в мкВ/°С. Типовые значения для биполярных входов 5 ...20 мкВ/°С, для входов с полевыми транзисторами 20 ...100 мкВ/°С.

Скорость нарастания выходного напряжения определяется как  $dU_{\text{вых}}/dt$  при воздействии импульса большой амплитуды. Измеряется в В/мкс. Для разных ОУ этот параметр меняется в пределах от 0,1 В/мкс (прецизионные ОУ) до 3000 В/мкс (быстродействующие ОУ). Этот параметр становится важным, если ОУ используется в качестве компаратора уровней сигналов в быстродействующих схемах.

$\mathcal{L}$ иапазон выходного напряжения ( $\Delta U_{\text{вых}}$ ) — диапазон значений выходного напряжения, при котором параметры ОУ лежат в гарантированных пределах.  $\Delta U_{\text{вых}}$  зависит от напряжения питания. Например, для ОУ 544УД2  $\Delta U_{\text{вых}}$  =10 В при  $U_{\text{п}}$  = ±15В.

Диапазон синфазных входных напряжений ( $U_{\rm вx.cф.}$ ) — такой диапазон синфазных входных напряжений, в котором параметры ОУ лежат в гарантированных пределах. Он зависит от напряжения питания.  $|U_{\rm вx.cф.}|$  примерно на  $2\dots 3$  В меньше  $|U_{\rm n}|$ .

Коэффициент ослабления синфазного сигнала равен отношению синфазного входного напряжения к дифференциальному входному напряжению, которые вызывают одно и то же  $U_{\rm вых}$ . Измеряется в децибелах. Для разных ОУ изменяется в пределах от 50 дБ (например, у ОУ 140УД5А) до 120 дБ.

Максимальный выходной ток ( $I_{\text{вых. max}}$ ). Это важный параметр, по существу определяющий нагрузочную способность ОУ. Для ОУ, имеющих внутреннюю защиту от короткого замыкания по выходу, это выходной ток короткого замыкания в режиме ограничения; для ОУ без защиты от короткого замыкания — предельный выходной ток, который нельзя превышать. У разных ОУ изменяется в диапазоне 1...1500 мА. У специализированных ОУ выходной ток может достигать нескольких ампер.

Кроме рассмотренных выше существуют также другие параметры, характеризующие ток потребления, шумовые, температурные, частотные, фазовые, временные и другие свойства ОУ. В конкретных применениях любой из этих параметров может стать самым важным и определяющим выбор типа ОУ. В таблице 1.1 приведены параметры некоторых ОУ отечественного производства.

Таблица 1.1 – Параметры некоторых ОУ отечественного производства

| Гип ОУ   | $K_0$<br>TbIC. | $U_{ m cM}$ [MB] | $\Delta U_{ m cm}/\Delta T$ [MKB/ $^{\circ}$ C] | $I_{ m BX} \ M_{ m BX}$ | $f_1$ [MF $\pi$ ] | $dU_{ m Bbix}/dt$ [ $B/_{ m MKC}$ ] | $K_{ m c \phi}$ [AB] | $\Delta U_{	ext{Bbix}}$ [B] | $R_{ m Bbix}$ [OM] | Inor<br>[MA] |

|----------|----------------|------------------|-------------------------------------------------|-------------------------|-------------------|-------------------------------------|----------------------|-----------------------------|--------------------|--------------|

| [40УД1Б  | 1,12           | 7                | 20                                              | 8000<br>1500            | 8                 | 0,8                                 | 09                   | +6.7/<br>-5.0               | 700                | 8            |

| 140УД5Б  | 2,5            | 5                | 9                                               | 0009<br>3000            | 14                | 9                                   | 09                   | +6.4/<br>-4.0               | 700                | 13           |

| 140УД7Б  | 45             | 10               | 50                                              | 550<br>200              | 0,8               | 0,3                                 | 70                   | 10                          | 150<br>20/кз       | 3,5          |

| 140УД708 | 30             | 9                | 300                                             | 400<br>200              | 0,8               | 0,3                                 | 70                   | 10,5                        | 200<br>20/кз       | 3,5          |

| 140УД8А  | 50             | 20               | 50                                              | 0.2<br>0.15             | 1                 | 5                                   | 64                   | 10                          | 200                | 5            |

| 140УД24  | 1000           | 0,005            | 0.05                                            | 0.01<br>0.005           |                   | 2,5                                 | 120                  | 4,7                         | 1 1                | 3.5          |

| 544УД1А  | 100            | 15               | 20                                              | 0.05<br>0.02            | 1                 | 5                                   | 80                   | 10                          | 200                | 3.5          |

| 544УД2Б  | 10             | 50               | 100                                             | 0.5<br>0.5              | 15                | 20                                  | 70                   | 10                          | 200<br>8           | 7            |

| 551УД1А  | 500            | 1,5              | 10                                              | 150                     | 0,8               | 0,01                                | 100                  | 5                           | - 5                | 5            |

| К553УД2  | 20             | 7,5              | 20                                              | 1500<br>500             | 1                 | 0,5                                 | 70                   | 10                          | 300                | 9            |

|          |                |                  |                                                 |                         |                   |                                     |                      |                             |                    |              |

#### 1.2 Типовые схемы включения операционного усилителя

Как уже было сказано выше, ОУ без обратной связи практически работать не может. В большинстве функциональных узлов, реализуемых на ОУ, используется глубокая отрицательная обратная связь (ООС). Исключение составляют схемы аналоговых компараторов и различные генераторы импульсов, в которых используется положительная обратная связь (ПОС). Влияние ООС на параметры функционального узла на ОУ более подробно рассмотрим ниже на примере инвертирующего усилителя.

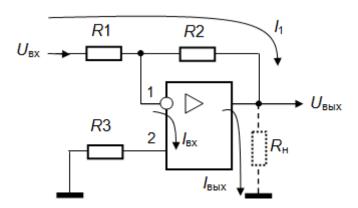

#### Инвертирующий усилитель

Принципиальная схема инвертирующего усилителя показана на рис. 1.4. Здесь и далее мы будем пользоваться упрощённым графическим изображением ОУ, (рис 1.2 б).

Рисунок 1.4 – Инвертирующий усилитель

Потенциал  $\phi$ 2 на неинвертирующем входе (в точке 2) можно считать равным нулю (ток через резистор R3 и, следовательно, падение напряжения на резисторе, ничтожно малы). Будем считать, что ОУ находится в линейном режиме усиления, т.е. не входит в режим насыщения ( $|U_{\text{вых}}| < |U_{\text{п}}|$ ).

Из основного уравнения ОУ (1.2) следует

$$\varphi 2 - \varphi 1 = U_{\text{вых}} / K_0$$

Пусть, например,  $U_{\text{вых}} \approx 5$  В,  $K_0 \approx 2 \times 10^5$ . Тогда получаем  $\phi 1 \approx 25$  мкВ. Такое малое напряжение невозможно измерить обычным цифровым вольтметром. Отсюда следует, что потенциалы на входах ОУ можно с с допустимой погрешностью считать равными, т.е.  $|\phi 2 - \phi 1| = |U_{1,2}| \approx 0$ . На основе сказанного выше можно сделать важный с практической точки зрения вывод (он справедлив не только для рассматриваемой схемы, но и для схемы любого функционального узла на ОУ с ООС):

При наличии отрицательной обратной связи разность потенциалов между дифференциальными входами ОУ близка к нулю.

Если один из входов ОУ заземлить, на втором входе будет также поддерживаться нулевой потенциал, т.е. для внешней (по отношению к ОУ) цепи входы 1 и 2 как бы соединены, хотя в действительности входы ОУ гальванически не связаны, и ток между входами 1 и 2 практически отсутствует. Этот эффект называется виртуальным или мнимым заземлением.

Таким образом, поскольку  $\varphi 2 = 0$ , то и  $\varphi 1 = 0$ . А поскольку входной ток ОУ очень мал ( $I_{\text{вх-}} << I_1$ ), им можно пренебречь, тогда получим

$$I_1 = \frac{U_{\text{BX}}}{R1} = -\frac{U_{\text{BMX}}}{R2}$$

Из этого следует, что для инвертирующего усилителя *коэффициент* усиления

$$K = \frac{U_{\text{BbIX}}}{U_{\text{DY}}} = -\frac{R2}{R1} , \qquad (1.3)$$

и, соответственно,

$$U_{\text{\tiny BMX}} = -\frac{R2}{R1}U_{\text{\tiny BX}},\tag{1.4}$$

#### Примечание.

- 1. При выводе выражений (1.3, 1.4) предполагалось, что выходное сопротивление источника сигнала  $R_{\text{вых (и.с.)}}$  (т.е. выходное сопротивление предшествующего звена электрической схемы) значительно меньше входного сопротивления рассматриваемого функционального узла. Если выходным сопротивлением источника сигнала пренебречь нельзя, то при выполнении расчётов величину этого сопротивления надо добавить к величине резистора R1, т.е.  $R1_{\text{экв.}} = R1 + R_{\text{вых (и.с.)}}$ .

- 2. Принципиально инвертирующий усилитель может работать и без резистора R3 (точка 2 может быть непосредственно «заземлена»). Резистор R3 используется для минимизации влияния токов смещения. Величина сопротивления этого резистора определяется из условия

$$R3 \approx R1 || R2 = \frac{R1 \cdot R2}{R1 + R2} \tag{1.5}$$

*Входное сопротивление* этой схемы равно  $R_{\rm BX~(y)}=R1$ , так как  $\phi_1=0$  (мнимое заземление). Ещё раз подчеркнём, что входное сопротивление функционального узла на ОУ не равно входному сопротивлению собственно ОУ  $(R_{\rm BX~(y)}\neq R_{\rm BX})$ .

Выходное сопротивление  $R_{\rm вых}\approx 0$ , так как  $R_{\rm вых}=dU_{\rm вых}/dI_{\rm вых}$ , а  $U_{\rm вых}$  в соответствии с выражением (1.4) от  $I_{\rm вx}$  не зависит. Таким образом, можно сделать ещё один важный с практической точки зрения вывод, справедливый для схемы любого функционального узла на ОУ с ООС:

При наличии отрицательной обратной связи выходное сопротивление функционального узла на ОУ близко к нулю.

Это не означает, конечно, что к выходу ОУ можно подключать нагрузку сколь угодно малого сопротивления, поскольку  $I_{\text{вых } max}$  реального ОУ ограничен условием обеспечения линейности режима его работы. При этом минимально допустимое сопротивление нагрузки определяется выражением

$$R_{\rm Hmin} = \frac{U_{\rm Bbix}}{I_{\rm DUM max}} \tag{1.6}$$

т.е. минимально допустимое сопротивление нагрузки на выходе ОУ зависит от амплитуды выходного напряжения.

Таким образом, идеализация ОУ ( $I_{\rm BX}=0$ ,  $K_0=\infty$ ) существенно облегчают анализ схем включения ОУ, а точный расчет добавляет только члены второго порядка малости. Например, более строгий вывод формулы для расчёта выходного сопротивления приводит к следующему результату

$$R_{\text{вых}} = \frac{R_{\text{вых}} \cdot (R1 + R2)}{R2 + (1 + K_0) \cdot R1} \approx \frac{R_{\text{вых}}}{K_0} \cdot \left(1 + \frac{R2}{R1}\right)$$

(1.7)

Пусть, например:  $R_{\text{вых (OY)}} = 200 \text{ Ом}$ ;  $K_0 = 2 \cdot 10^5$ ; R2/R1 = 10.

Тогда получим:  $R_{\rm вых} \approx 10^{-2} {\rm Om}$  (примерно такое сопротивление имеет медный провод диаметром 0,3 мм и длиной всего 5 см!).

Очевидно, что в нашем случае таким сопротивлением можно пренебречь. Следовательно,  $R_{\text{вых}} \approx 0$ .

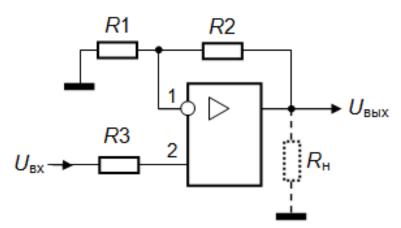

#### Неинвертирующий усилитель

Как видно из рис. 1.5 входной сигнал подаётся на неинвертирующий вход (точка 2), а на инвертирующий вход (точка 1) подаётся напряжение, снимаемое с делителя на резисторах R2, R1.

Рисунок 1.5 – Неинвертирующий усилитель

Обозначим через  $U_1$  напряжение между точкой 1 и общим проводом («землёй»).

$$U_1 = \frac{U_{\text{\tiny BbIX}} \cdot R1}{(R1 + R2)}.$$

Поскольку, как было показано выше, потенциалы точек 1 и 2 при наличии ООС практически равны, то входное напряжение  $U_{\rm Bx}$  =  $U_{\rm 1}$ . Из этого следует, что коэффициент усиления неинвертирующего усилителя равен

$$K = \frac{U_{\text{BMX}}}{U_{\text{RY}}} = 1 + \frac{R2}{R1} \,. \tag{1.8}$$

Входное сопротивление неинвертирующего усилителя

$$R_{\text{\tiny BX}} = R_{\text{\tiny gx(OV)}} \cdot K_0 \cdot \frac{R1}{(R1 + R2)}$$

т.е значительно больше входного сопротивления ОУ.

Выходное сопротивление  $R_{\text{вых}} \approx 0$ .

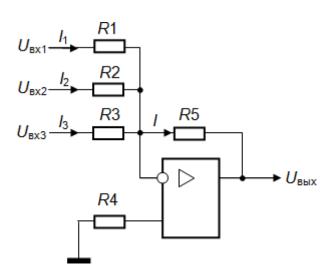

#### Аналоговый сумматор

В соответствии с первым законом Кирхгофа можно считать, что  $I_1+I_2+I_3=I$  (напомним, что входным током ОУ можно пренебречь), и с учётом выражения (1.4) можно записать

$$U_{\text{вых}} = -R5 \cdot \left( \frac{U_{\text{вх1}}}{R1} + \frac{U_{\text{вх2}}}{R2} + \frac{U_{\text{вх3}}}{R1} \right) \tag{1.9}$$

При этом очевидно, что если R1=R2=R=R, то выходной сигнал будет пропорционален сумме входных сигналов

$$|U_{\text{bbx}}| = \frac{R5}{R} |U_{\text{bx}1} + U_{\text{bx}2} + U_{\text{bx}3}|$$

(1.10)

Рисунок 1.6 – Аналоговый сумматор

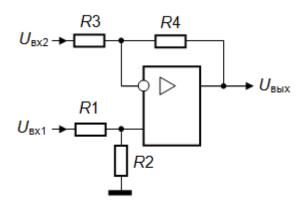

#### Дифференциальный усилитель (схема вычитания)

Дифференциальный усилитель представляет собой сочетание инвертирующего и неинвертирующего усилителей. Можно доказать, что

$$U_{\text{вых}} = \frac{U_{\text{вх1}} \cdot R2}{R1 + R2} \left( 1 + \frac{R4}{R3} \right) - U_{\text{вх2}} \frac{R4}{R3}$$

(1.11)

Если R1 = R3 и R2 = R4, то получим более простую формулу

$$U_{\text{вых}} = (U_{\text{вх1}} - U_{\text{єx2}}) \frac{R4}{R3} \tag{1.12}$$

Рисунок 1.7 – Дифференциальный усилитель

Таким образом, дифференциальный усилитель увеличивает разность входных напряжений в *R*4/*R*3 раз.

#### Буферный каскад (повторитель)

Коэффициент передачи буферного каскада равен 1. Это означает, выходной сигнал повторяет входной  $U_{\rm вых} = U_{\rm вx}$ .

На первый взгляд простое повторение входного сигнала не имеет смысла. В действительности такая схема включения ОУ используется довольно часто. Причина в том, буферный каскад одновременно обладает очень большим входным сопротивлением и практически нулевым выходным сопротивлением.

$$R_{ex} \approx \infty, \ R_{\text{Bbix}} = 0.$$

(1.13)

Рисунок 1.8 – Буферный каскад

Таким образом, буферный каскад фактически играет роль не усилителя напряжения, а усилителя мощности источника сигнала. И, следовательно, позволяет подключать выход функционального узла, обладающего высоким выходным сопротивлением, ко входу функционального узла с низким входным сопротивлением.

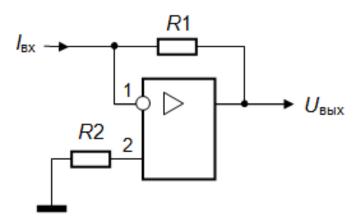

#### Преобразователь ток-напряжение

Схема преобразователя ток-напряжение напоминает схему инвертирующего усилителя (см. рис. 1.4), в котором отсутствует входной резистор (на рис. 1.4 он обозначен R1). Отсутствие входного резистора превращает схему инвертирующего усилителя в принципиально другой

функциональный узел — преобразователь входного тока в выходное напряжение. Нетрудно доказать, что коэффициент преобразования входного сигнала (в виде тока) в выходной сигнал (в виде напряжения) определяется приближённым выражением

$$|U_{\text{вых}}| \approx |I_{\text{вх}}| \cdot R_{\text{ooc}} \, [\text{B/A}]$$

где  $R_{\text{ooc}} = R1$  — сопротивление обратной связи.

Рисунок 1.9 – Преобразователь ток-напряжение

Входное сопротивление такой схемы очень мало  $R_{\rm BX} \approx R_{\rm ooc}/K_0$  (1.15)

Применение преобразователя ток-напряжение целесообразно в тех случаях, когда источник сигнала обладает очень большим выходным сопротивлением, и поэтому его выгодно рассматривать не как источник напряжения (при  $R_{\text{вых}} \approx 0$ ) , а как источник тока (при  $R_{\text{вых}} \approx \infty$ ). Хорошим примером является фотоприёмный узел на основе пары фотодиод — операционный усилитель (см. раздел 1.3).

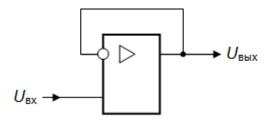

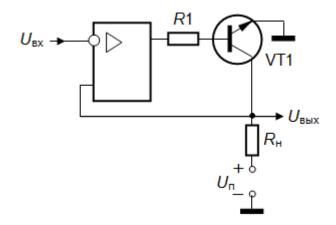

#### Схема включения ОУ с обращением входов

Такая схема может быть полезной, когда требуется управлять большим током нагрузки (резистор  $R_{\rm H}$ ), т.е. током, который превышает нагрузочную способность ОУ. В данном случае напряжение обратной связи, снимаемое с коллектора транзистора VT 1, подаётся на неинвертирующий вход ОУ. Таким образом, входы ОУ как бы меняются ролями. Однако и в данной схеме включения реализуется не положительная, а отрицательная обратная связь, поскольку функцию инвертора выполняет транзистор, включённый по схеме с общим эмиттером. В целом рассматриваемая схема функционирует как повторитель, в котором напряжение на коллекторе VT 1 следует за напряжением на входе.

Рисунок 1.10 – Схема с обращением входов

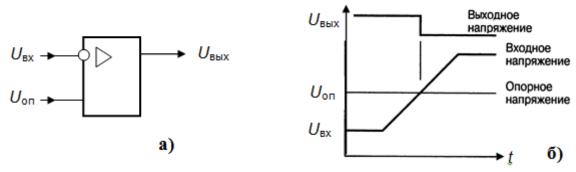

#### Аналоговый компаратор

Простейший аналоговый компаратор (схема сравнения напряжений) показан на рис. 1.11 а. Он представляет собой ОУ без обратной связи. Принцип его работы поясняет рис. 1.11 б.

Однако на практике такой компаратор используется крайне редко. Основной его недостаток — неустойчивая работа при медленном при-ближении входного сигнала к опорному напряжению, т.к. из-за наличия шумов во входном сигнале возможны ложные переключения.

Рисунок 1.11 – Простейший аналоговый компаратор (a); временные диаграммы, поясняющие принцип его работы (б)

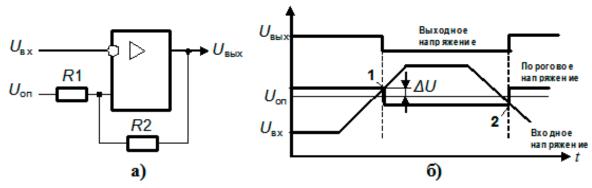

На рис. 1.12 а приведена схема компаратора с добавлением цепи *гистерезиса*.

Как видно из рис. 12 б переключение выходного напряжения происходит при различных уровнях (точки 1 и 2) в зависимости от характера изменения входного сигнала (возрастание или убывание). Это позволяет исключить ложные срабатывания компаратора, если уровень шумов во входном сигнале не превышает величины  $\Delta U$ .

Рисунок 1.12 – Аналоговый компаратор с гистерезисом (a); временные диаграммы, поясняющие принцип его работы (б)

Нетрудно показать, что, например, при однополярном питании ОУ величина  $\Delta U$  определяется выражением

$$\left|\Delta U\right| = \frac{\left(U_{\text{вых max}} - U_{\text{on}}\right) \times R1}{R1 + R2}$$

(1.16)

где  $U_{\text{вых max}}$  — максимальное значение выходного напряжения, соответствующее уровню насыщения ОУ.

Пусть, например,  $U_{\rm вых\ max}=5$  B;  $U_{\rm on}=2.5$  B; R1=1 кОм; R2=100 кОм. Тогда  $\Delta U=0.0247$  B. А полная «ступенька» гистерезиса (U1-U2, рис. 1.12) составит приблизительно 0.05 B.

При двухполярном питании ( $U_{\text{вых max}} = 5 \text{ B}$ ;  $U_{\text{вых min}} = -5 \text{ B}$ ) и таких же величинах R1, R2 получим  $\Delta U_{+} = 0.0247$ ;  $\Delta U_{-} = -0.074 \text{ B}$ . Однако асимметрия «ступеньки» гистерезиса при двухполярном питании ОУ на практике не всегда является существенным недостатком.

Заметим, что среди рассмотренных в данном разделе возможных схем включения ОУ это единственная схема, в которой используется не отрицательная, а положительная обратная связь. В данном случае положительная обратная связь не только позволяет реализовать функцию гистерезиса, но и увеличивает скорость переключения, способствуя повышению быстродействия аналогового компаратора.

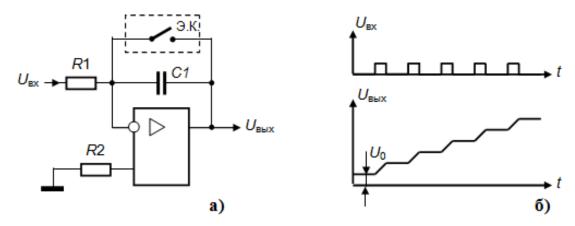

#### Интегрирующий усилитель (аналоговый интегратор)

Рассмотрим схему, приведённую на рис.1.13. С учётом мнимого заземления (см. выше) можно записать

$$I_{\text{BX}} = I_{RI} = U_{\text{BX}} / R1 = I_{C1} = C1 \cdot dU_{CI} / dt$$

.

Тогда с учетом полярности  $U_{C1}$ , получим

$$U_{\text{вых}} = -\frac{1}{R1 \cdot C1} \int U_{\text{вх}} \cdot dt + U_0 , \qquad (1.17)$$

где  $U_0$  — напряжение на выходе при t=0. ( $U_0 \neq 0$ , если емкость C1 была заряжена перед началом интегрирования).

Рисунок 1.13 – Аналоговый интегратор (а); пример временных диаграмм, поясняющих принцип его работы (б)

Нулевое начальное условие  $(U_0=0)$  можно задать при помощи управляемого электронного ключа (Э.К.). Обычно  $R1>>r_{\rm к.r.}$  ( $r_{\rm к.r.}$ —сопротивление замкнутого электронного ключа, от единиц до десятков Ом). Таким образом, при замкнутом ключе  $U_{\rm вых}=U_{C1}=0$ , а при разомкнутом идет интегрирование. Точность вычисления интеграла зависит от коэффициента усиления  $K_0$ , от величины входных токов, от напряжением смещения  $U_{\rm cm}$  и других параметров ОУ. Для интеграторов обычно используются ОУ с полевыми транзисторами на входе и конденсаторы с малыми токами утечки.

Интеграторы могут использоваться в качестве функциональных узлов электронного тракта ОЭП или входить в состав аналоговых вычислительных машин. С их помощью можно решать обыкновенные дифференциальные уравнения, в том числе нелинейные.

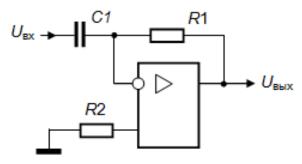

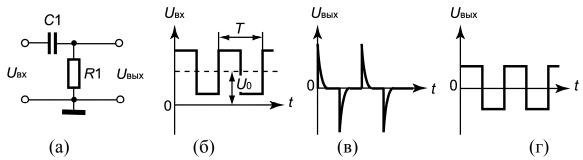

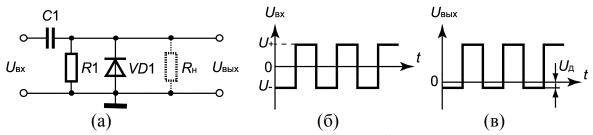

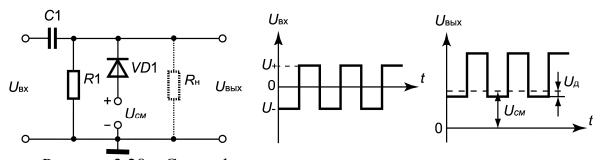

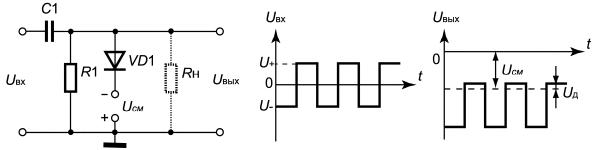

#### Дифференцирующий усилитель

Если на схеме, показанной на рис 1.13 поменять местами R1 и C1, то получим узел, выполняющий обратную операцию функцию — функцию дифференцирования входного сигнала.

$$U_{\text{вых}} = -R1 \cdot C1 \cdot \frac{dU_{\text{вх}}}{dt} \tag{1.18}$$

Рисунок 1.14 – Дифференцирующий усилитель

Однако в таком упрощённом виде (без специальных цепей коррекции) эта схема сравнительно редко используется на практике, так как обладает слишком большим коэффициентом передачи на высоких частотах и потому заметно усиливает импульсные наводки и собственные шумы.

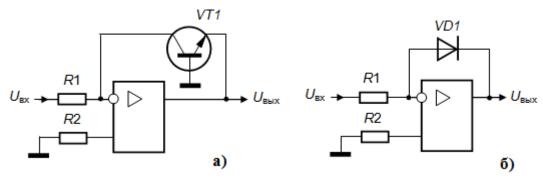

#### Логарифмический усилитель

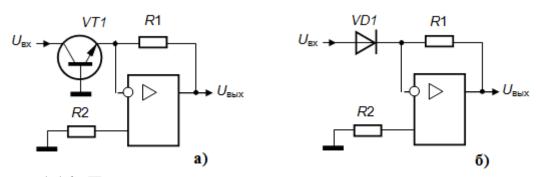

*Погарифмический усилитель* (рис. 1.15) может использоваться для получения логарифмической зависимости  $U_{\text{вых}} \sim \lg(U_{\text{вх}})$ . Для этого в цепь отрицательной обратной связи ОУ вводят нелинейный элемент — диод или биполярный транзистор.

Рисунок 1.15 – Логарифмический усилитель с использованием транзистора (a) или диода (б) в цепи отрицательной обратной связи

Рассмотри подробнее схему, показанную на рис 1.15 а.

Ток, протекающий в цепи отрицательной обратной связи, при  $I_{\rm BX}=0$ , равен коллекторному току транзистора и определяется равенством

$$I_{\text{BX}} = \frac{U_{\text{BX}}}{R1} = I_{\text{K}} = I_{\text{K0}} \left[ \exp \left( \frac{q_e \cdot U_{96}}{\eta \cdot k \cdot T} \right) - 1 \right]$$

(1.19)

где  $I_{\rm K0}$  — тепловой ток p-n перехода (обратный ток коллектора);  $U_{\rm 96}$  — напряжение на переходе эмиттер-база; k — постоянная Больцмана; T — температура в градусах Кельвина; q — заряд электрона;  $\eta$  - постоянная рекомбинации.

Величина  $\eta kT/q_e = \phi_{\scriptscriptstyle T}$  называется температурным потенциалом; (например, для германия  $\phi_{\scriptscriptstyle T} \approx 26$  мВ, для кремния  $\phi_{\scriptscriptstyle T} \approx 30$  мВ). Заметим, что для большинства биполярных транзисторов малой мощности  $I_{\rm K0} < 10^{-8}$  А, т.е.  $I_{\rm K0} << I_{\rm K}$ , и, следовательно, «единицей» в квадратных скобках в выражении (1.19) можно пренебречь. С учётом вышесказанного и принимая во внимание, что  $U_{\rm вых} = U_{\rm 96}$  можно записать

$$U_{\text{\tiny gbix}} \approx \varphi_{m} \left[ \ln(I_{\text{\tiny K}}) - \ln(I_{\text{\tiny K0}}) \right] = \varphi_{m} \left[ \ln\left(\frac{U_{\text{\tiny BX}}}{K}\right) - \ln(I_{\text{\tiny K0}}) \right]$$

(1.20)

Логарифмический усилитель часто применяются для расширения диапазона измеряемых токов и потому в них используются ОУ с полевыми

транзисторами. которые тщательно балансируют. Это позволяет к тому же свести к нулю и второй член в выражении (1.20). С помощью логарифмического усилителя можно также возводить в произвольную степень и перемножать аналоговые сигналы. Однако схемы, приведенные на рис. 1.15 работают только с однополярными (в данном примере положительными) сигналами.

Погрешность логарифмического усилителя может достигать порядка нескольких процентов. Снижения погрешности можно добиться путём компенсации температурного дрейфа и стабилизации температуры.

#### Потенцирующий усилитель

**Поменцирующий усилимель** может использоваться для получения степенной зависимости  $U_{\text{вых}}$ -exp( $U_{\text{вх}}$ ). Он получается, если резистор и транзистор (диод) в цепи обратной связи поменять местами (рис. 1.16). При этом все рассуждения аналогичны рассуждениям, сделанным выше.

Рисунок 1.16— Потенцирующий усилитель с использованием с транзистора (a) или диода (б) в цепи отрицательной обратной связи

Рассмотренные типовые схемы представляют лишь небольшую часть возможных вариантов использования ОУ при реализации узлов обработки аналоговых сигналов. Приведённые выше функциональные зависимости в случаев основаны на упрощённом большинстве представлении параметрах почти идеального ОУ (1.1). Во многих случаях такое упрощение вполне допустимо. Однако при оценке предельных возможностей тех или иных функциональных узлов, а также при обосновании ограничений, возникающих при выборе элементов электрической схемы, необходим более точный учёт параметров реального ОУ. Ниже это проиллюстрировано в частности на примере фотоприёмного узла, входящего в структуру оптико-электронного датчика, решающего задачу измерения координат изображения целевой марки (разделы 1.4 – 1.5). Более подробно вопросы учёта параметров реального ОУ при построении различных функциональных узлов освещены, например, в работах [3, 4, 5].

#### 1.3 Электронные ключи и коммутаторы аналоговых сигналов

#### 1.3.1 Общие определения

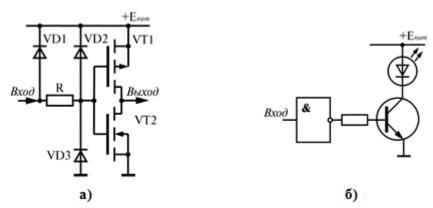

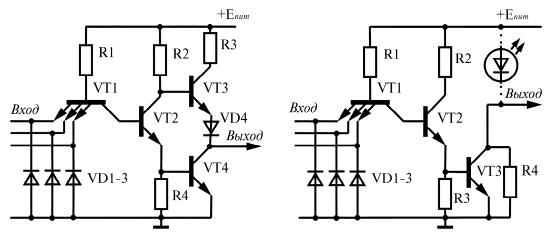

Электронные ключи и коммутаторы входят в состав различных функциональных узлов и модулей аппаратных средств электронного тракта оптико-электронных приборов и систем. С их помощью осуществляется управление источниками излучения, электромагнитными реле, шаговыми двигателями; они являются основными компонентами аналоговых мультиплексоров и демультиплексоров, цифро-аналоговых преобразователей, узлов выборки и хранения и др.

Электронные ключи, которые в зависимости от управляющего сигнала обеспечивают один из двух уровней выходного напряжения, относятся к категории *цифровых* или *бинарных* коммутаторов. Электронные ключи и коммутаторы, которые служат для включения, выключения или переключения непрерывно изменяющихся электрических сигналов в виде токов или напряжений – к категории *аналоговых*.

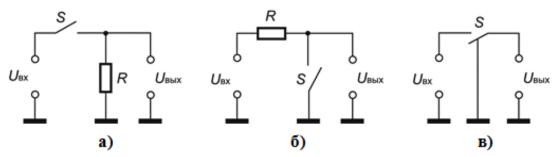

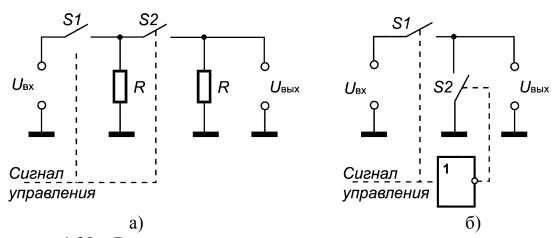

Если электронный коммутатор находится в состоянии «включено», его выходное напряжение должно, по возможности, быть равным входному; если же коммутатор находится в состоянии «выключено», выходное напряжение должно быть как можно ближе к нулю. Существуют различные схемные решения коммутаторов, удовлетворяющие указанным условиям. Их принцип действия показан на рис. 1.17 на примере механических переключателей.

На рис. 1.17 а представлен последовательный коммутатор. Пока контакт замкнут,  $U_{\text{вых}} = U_{\text{вх}}$ . Когда контакт размыкается, выходное напряжение становится равным нулю. Это справедливо, если источник сигнала имеет нулевое выходное сопротивление, а емкость нагрузки равна нулю. При значительном выходном сопротивлении источника сигнала напряжение  $U_{\text{вых}}$  делится между этим сопротивлением и резистором R. Поэтому данную схему не следует применять в случае, если источником сигнала является источник тока, например, фотодиод. При существенной емкости нагрузки во время разряда этой емкости при размыкании ключа S выходное напряжение коммутатора падает до нуля с задержкой.

Рисунок 1.17 – Схемные решения коммутаторов

В схеме параллельного коммутатора (рис. 1.176)  $U_{\text{вых}} = U_{\text{вх}}$  при разомкнутом ключе, если входное сопротивление нагрузки коммутатора бесконечно велико. Если же оно соизмеримо с сопротивлением резистора R, то на резисторе будет падать часть выходного напряжения источника сигнала. При наличии емкостной нагрузки выходное напряжение будет устанавливаться после размыкания ключа относительно медленно. Последовательно-параллельный коммутатор, показанный на рис. 1.17 в, не имеет недостатков двух предыдущих схем. В любом рабочем состоянии он имеет выходное сопротивление, близкое к нулю.

Разновидности электронных коммутаторов, показанные на рис. 1.17, могут быть реализованы на электронных элементах с управляемым сопротивлением, имеющим малое минимальное и высокое максимальное значения. Для этих целей могут использоваться *биполярные* и *полевые* транзисторы.

Сравнивая электронные ключи на биполярных и полевых транзисторах, следует отметить преимущества и недостатки каждого из них.

Ключи на биполярных транзисторах требуют большей мощности по цепям управления и имеют сравнительно большое остаточное напряжение, составляющее единицы милливольт. Это вносит заметную погрешность при коммутации слабых сигналов (менее 100 мВ). Однако благодаря малому времени переключения такие ключи широко используются для построения быстродействующих коммутаторов при переключении сигналов с уровнем более 100 мВ.

По быстродействию ключи на полевых транзисторах обычно уступают ключам на биполярных транзисторах. Кроме того у них наблюдается проникновение в коммутируемую цепь импульсных помех от управляющих сигналов. К числу преимуществ следует отнести: меньшее остаточное напряжение на ключе в проводящем состоянии при достаточно высоком непроводящем В состоянии, малую мощность от источника управляющих сигналов, а также хорошую электрическую развязку между источником управления и источником коммутируемого сигнала. Указанные достоинства делают возможным использование ключей на полевых транзисторах для коммутации электрических сигналов низкого уровня (порядка микровольт).

#### 1.3.2 Особенности работы ключей на биполярных транзисторах

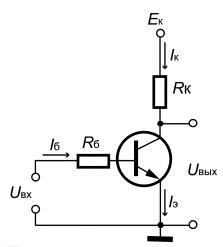

Ключ на биполярном транзисторе по схеме включения подобен однокаскадному транзисторному усилителю с общим эмиттером [5]. Однако по выполняемым функциям и режимам работы активного элемента он существенно отличается усилительного каскада.

Транзисторный ключ (ТК) имеет два основных состояния: *режим отсечки*, когда транзистор заперт, и *режим насыщения*, при котором

транзистор полностью открыт или находится в состоянии близком к этому. В течение короткого процесса переключения транзистор работает в активном линейном режиме. В целом же процессы в ключевом каскаде носят нелинейный характер.

Рисунок 1.18 – Простой ключ на биполярном транзисторе

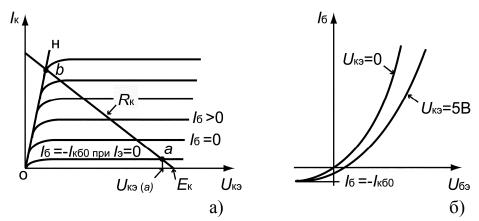

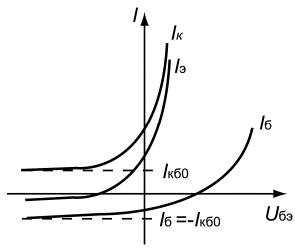

Поведение ТК определяется его статическими характеристиками. При их анализе обычно используется семейство выходных  $I_{\kappa}(U_{\kappa_3})$  и входных  $I_{\delta}(U_{\delta_3})$  характеристик транзистора (рис. 1.19 а, б).

**В режиме отсечки** коллекторный и эмиттерный переходы биполярного транзистора должны быть смещены в обратном направлении (т.е. заперты для основных носителей заряда). В этом режиме через транзистор протекают лишь очень малые токи неосновных носителей. На выходных характеристиках такому состоянию транзистора соответствует точка «а». При этом напряжение на коллекторе

$$U_{\text{K3(a)}} = E_{\text{K}} - I_{\text{K60}} \cdot R_{\text{K}} \approx E_{\text{K}},$$

где  $I_{\kappa 60}$  — обратный ток коллекторного перехода (ток неосновных носителей).

Рисунок 1.19 – Выходные (а) и входные (б) характеристики транзистора

Поскольку ток эмиттера в данном случае очень мал и практически равен нулю [5], сопротивление транзистора в режиме отсечки

$$R_{\rm T} = U_{\rm K9(a)}/I_{\rm K60} \approx E_{\rm K}/I_{\rm K60}.$$

Это сопротивление, как правило, достаточно велико (> 100 кОм).

В быстродействующих ключах сопротивление  $R_{\kappa}$  в цепи коллектора берут небольшим (порядка единиц кОм) для уменьшения постоянной времени, связанной с перезарядкой паразитных ёмкостей. Поэтому выходное сопротивление ТК в основном определяется именно коллекторным сопротивлением транзистора

$$R_{\text{BMX TK}} = R_{\text{K}} \parallel R_{\text{T}} \approx R_{\text{K}}. \tag{1.21}$$

При приближении к нулю запирающего входного управляющего напряжения ( $U_{\rm Bx} \to 0$ ) транзистор продолжает оставаться запертым, хотя и выходит из режима глубокой отсечки, однако его токи несколько изменяются. При этом ток базы изменяется очень мало и практически остаётся на уровне  $I_6 \approx -I_{\rm кбо}$ , в то время как ток эмиттера на границе отсечки существенно увеличивается и меняет знак. Изменение трёх токов на границе режима отсечки показаны на рис. 1.20.

Рисунок 1.20– Токи транзистора на границе режима отсечки

С практической точки зрения важно иметь в виду, что глубина отсечки зависит не только от уровня управляющего сигнала  $U_{\rm Bx}$  но и от сопротивления резистора, включённого в цепь базы. Это связано с тем, что ток обратно смещенных переходов, протекающий в базовой цепи, создаёт дополнительное падение напряжение на сопротивлении  $R_{\rm 6}$ . При этом напряжение между базой и эмиттером транзистора отличается от  $U_{\rm Bx}$

$$U_{69} = U_{\text{BX}} + I_{\text{K}60} \cdot R_6. \tag{1.22}$$

Таким образом, даже при некотором отрицательном напряжении источника управляющего сигнала  $U_{\rm Bx} < 0$  (сигнал запирания ключа) напряжение  $U_{\rm 69}$  может оказаться > 0, и транзистор перейдёт в активный режим, сопровождающийся появлением значительных токов  $I_{\rm K}$  и  $I_{\rm 3}$ . Поэтому для

надёжного запирания транзистора в режиме отсечки сопротивление резистора в цепи базы следует выбирать из условия

$$|I_{\kappa\delta0}| \cdot R_6 < |U_{\rm BX}|. \tag{1.23}$$

В свою очередь сопротивление резистора в цепи коллектора должно удовлетворять неравенству

$$I_{\kappa \delta o} \cdot R_{\kappa} \ll E_{\kappa}. \tag{1.24}$$

Причём в выражениях (1.23) и (1.24) следует принимать в расчет максимальную величину тока  $I_{\kappa\delta0}$ , соответствующую наивысшей рабочей температуре.

**В режиме насыщения** оба *p-n* перехода транзистора смещены в прямом направлении (т.е. открыты для основных носителей заряда). При этом напряжение  $U_{\kappa 9}$  ТК мало по сравнению с  $E_{\kappa}$  и обычно составляет десятки мВ. На выходных характеристиках (рис. 1.19) линия ОН характеризует область насыщения транзистора. Каждой точке этой линии соответствует некоторое граничное значение напряжения  $U_{\kappa} = U_{\kappa \text{ нас}}$ , тока  $I_{\kappa} = I_{\kappa \text{ нас}}$ , и тока  $I_{6} = I_{6 \text{ нас}}$ . Токи  $I_{\kappa \text{ нас}}$  и  $I_{6 \text{ нас}}$  называются соответственно коллекторным и базовым токами насыщения. Таким образом,  $U_{\kappa \text{ нас}}$  и  $I_{\kappa \text{ нас}}$  связаны между собой линейной зависимостью

$$R_{\text{Hac}} = U_{\text{K Hac}} / I_{\text{K Hac}}, \tag{1.25}$$

где  $R_{\text{нас}}$  — сопротивление насыщенного транзистора, которое характеризуется крутизной линии насыщения ОН. Обычно величина  $R_{\text{нас}}$  достаточно мала и составляет десятки или сотни Ом.

Режим насыщения транзистора обусловлен тем, что максимальный ток коллектора ТК ограничен напряжением источника питания и сопротивлением  $R_{\rm K}$ .

$$I_{\kappa max} = I_{\kappa hac} \le E_{\kappa} / R_{\kappa} . \tag{1.26}$$

Так как в режиме насыщения напряжение  $U_{\mbox{\tiny K}3}$  ТК мало по сравнению с  $E_{\mbox{\tiny K}}$ , то

$$I_{\kappa max} = I_{\kappa Hac} \approx E_{\kappa}/R_{\kappa}. \tag{1.27}$$

Для оценки глубины насыщения используют понятие коэффициента насыщения, который показывает, во сколько раз реальный ток базы превышает ток, необходимый для достижения режима насыщения

$$S = I_6 / I_{6 \text{ Hac}}$$

(1.28)

Заметим, что в режиме насыщения сопротивление транзистора  $R_{\rm T}$  минимально и практически не зависит от  $I_{\rm G}$  и  $R_{\rm G}$ . Это сопротивление и является выходным сопротивлением ТК в замкнутом состоянии. Начиная от значений S=2 и выше, сопротивление ТК мало зависит от тока базы, поэтому более высокую степень насыщения применять нецелесообразно.

Очень слабая зависимость тока коллектора от температуры является большим преимуществом режима насыщения.

Требуемый ток базы, обеспечивающий заданный уровень насыщения

$$I_6 = (U_{\rm BX} - U_{\rm 69})/R_6 = S \cdot I_{\rm K \ Hac}/\beta = S(E_{\rm K} - U_{\rm K \ Hac})/\beta \cdot R_{\rm K}$$

, (1.29)

где  $U_{69} = (0,7...0,8)$  В — напряжение база-эмиттер открытого транзистора (имеются в виду кремниевые транзисторы); S — коэффициент насыщения;  $\beta = (50...300)$  — коэффициент усиления транзистора по току;  $U_{\text{к нас}} = (0,1...0,2)$  В — напряжение на коллекторе открытого транзистора.

Пусть в качестве примера ТК управляется сигналом, снимаемым с выхода микросхемы транзисторно-транзисторно логики (ТТЛ) и использует то же питающее напряжение  $E_{\rm K}=5$  В. Для микросхем ТТЛ минимальное выходное напряжение, соответствующее уровню логической единицы (сигнал отпирания для ТК) составляет  $U_{\rm Bx\,(1)}=2,4$  В. Тогда при наихудшем сочетании параметров микросхемы ТТЛ требуемое сопротивление резистора в цепи базы составит

$$R_6 = \beta \cdot R_{\kappa} (U_{\text{BX}} - U_{\text{fig}}) / S(E_{\kappa} - U_{\kappa \text{ Hac}}) = 0.17 \beta \cdot R_{\kappa}.$$

(1.30)

Важным параметром ТК является время включения и выключение, после поступления соответствующего управляющего сигнала. Оно характеризует быстродействие, т.е. максимальную частоту следования импульсов управляющего сигнала. Время переключение ТК зависит от общей длительности переходного процесса, который в свою очередь определяется инерционностью процессов, протекающих в транзисторе (например, рекомбинация основных носителей заряда), а также перезарядом паразитных ёмкостей. Уменьшить влияние последнего фактора можно путём подключения конденсатора параллельно резистору  $R_{\delta}$  (рис. 1.21 a). Этот конденсатор, называемый ускоряющим, увеличивает отпирающий базовый ток в момент появления сигнала логической единицы, ускоряя процесс отпирания. Он же ускоряет процесс запирания транзистора при поступлении сигнала логического нуля, поскольку в этом случае в процессе перезаряда конденсатор будет создавать на базе запирающее напряжение отрицательной полярности.

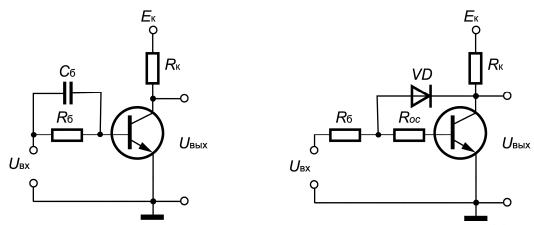

Рисунок1.21 – Примеры ТК с ускоряющим конденсатором (a); с отрицательной обратной связью (б)

Другой эффективный способ повышения быстродействия ТК заключается в применении диода VD в цепи нелинейной отрицательной

обратной связи, предотвращающей насыщение транзистора (рис. 21б). Пока транзистор заперт, и, следовательно, напряжение база-коллектор больше падения напряжения на сопротивлении  $R_{\rm oc}$  диод заперт и отрицательная обратная связь не действует. При увеличении входного сигнала увеличивается ток коллектора и уменьшается напряжение на коллекторе. Диод VD отпирается и начинает действовать отрицательная обратная связь. Дальнейший рост входного тока престаёт влиять на режим работы транзистора, т.к. основная его часть протекает через диод и транзистор, который хотя и открыт, но не переходит в режим насыщения. Существенного повышения быстродействия удаётся достичь только при использовании диодов, имеющих малое время восстановления. В случае применения низкочастотных диодов эффект от введения нелинейной обратной связи будет незначителен. К основным недостаткам ненасыщенного транзисторного ключа следует отнести:

- большее падение напряжение на открытом ключе ( $\approx 0.5 \, \mathrm{B}$ );

- меньшую помехоустойчивость;

- значительно большую, чем у насыщенного ключа, температурную нестабильность.

Рисунок 1.22 – Примеры ТК с компенсирующим источником базового тока

Заметим, что максимальное напряжение, соответствующее логическому нулю на выходе микросхемы ТТЛ (сигнал запирания для ТК) в худшем случае может достигать +0,2 В. К этому добавляется падение напряжения на резисторе  $R_6$ , обусловленное прохождением коллекторного теплового тока  $I_{\kappa 60}$ . Поэтому транзистор будет закрыт не полностью. В результате величина тока, протекающего через ТК в режиме запирания может в 3...5 раз превышать  $I_{\kappa 60}$  (см. рис.1.20). В некоторых случаях это не вызывает проблем, например, при управлении электромагнитными реле или шаговыми двигателями, т.к. для их срабатывания требуются значительно большие токи. При необходимости же достижения режима глубокой

отсечки, в схеме ТК следует использовать дополнительный компенсирующий источник  $U_{6\kappa} \approx 0,3...0,5$  В совместно с резистором  $R_{6\kappa} \approx R_6$  для обеспечения условий надёжного запирания транзистора (рис. 1.22) при воздействии на его управляющий вход сигнала логического нуля с выхода микросхемы ТТЛ.

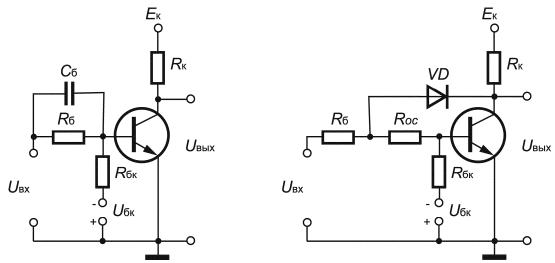

Электронный ключ, рассмотренный выше, обеспечивает один из двух уровней выходного напряжения. Он относятся к категории цифровых или бинарных коммутаторов. На его основе можно реализовать ключевую цепь для коммутации аналоговых, в том числе разнополярных, сигналов (рис. 1.23a).

Рисунок 1.23 – Схема (а) и характеристики (б) аналогового ключа

В приведённой выше схеме роль источника питающего напряжения  $E_{\rm k}$  играет коммутируемое напряжение  $U_{\rm bx}$ . Чтобы при любых изменениях полярности и допустимой величины входного коммутируемого сигнала p-n переходы транзистора оставались запертыми необходимо, чтобы при подаче запирающего управляющего напряжения  $U_{\rm v}$  выполнялось условие

$$|U_{\mathrm{y}}| > |U_{\mathrm{BX}\;max}|$$

.

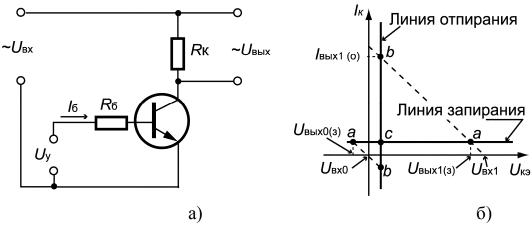

Если ключ заперт по цепи базы отрицательным управляющим напряжением ( $U_{69} = U_{\rm y} < 0$ ), то при всех значениях входного напряжения, при которых  $|U_{\rm k9}| < U_{\rm y}$ , в выходной цепи протекает ток, близкий к  $I_{\rm k60}$ , и характеристика  $I_{\rm k}(U_{\rm k9})$  идёт почти горизонтально (рис. 1.23 б). Назовём эту линию, по которой перемещается точка «a» линией запирания.

При изменении полярности управляющего напряжения ( $U_{69} = U_{\rm y} > 0$ ) транзистор откроется. Если при этом  $I_6 > I_{\rm 6~Hac} = const$ , то падение напряжение на транзисторе мало, и характеристика  $I_{\rm K}$  ( $U_{\rm K9}$ ) идёт почти вертикально. Назовём эту линию, по которой перемещается точка «b» линией отпирания. В идеальном аналоговом ключе линии запирания и отпирания совпадали бы с осями координат. В реальном ключе эти линии имеют небольшой наклон, а точка их пересечения «c» не совпадает с началом координат

$$I_c \approx I_{\kappa 60} + (U_y/R_3);$$

$$U_c = I_c \cdot R_H,$$

(1.31)

где  $R_3$  — сопротивление закрытого ключа.

Пунктирная линия, проходящая через точки «*a*» и «*b*» (рис. 23б), является своего рода условной «траекторией», по которой перемещается рабочая тока во время переходного процесса переключении ТК. Тангенс угла наклона этой линии по отношению к оси абсцисс  $tang \phi = 1/R_{\rm H}$ .

Наклон линии запирания обусловлен конечностью величины сопротивления закрытого ключа  $R_3$ , которое учитывает ток утечки, токи термогенерации в p-n переходе и др. Наклон линии запирания, как правило, весьма мал, поскольку обычно величина  $R_3 > 1$  Мом. Наклон линии отпирания определяется сопротивлением транзистора в режиме насыщения, которое у маломощных транзисторов не превышает нескольких десятков Ом.

Таким образом, реальному транзисторному ключу свойственны два вида погрешностей: сдвига и наклона. Степень влияния этих погрешностей уменьшается с увеличением входного сигнала.

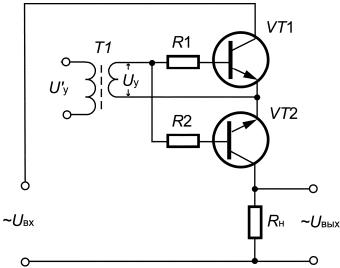

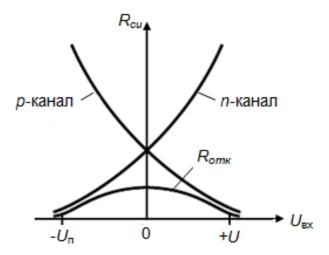

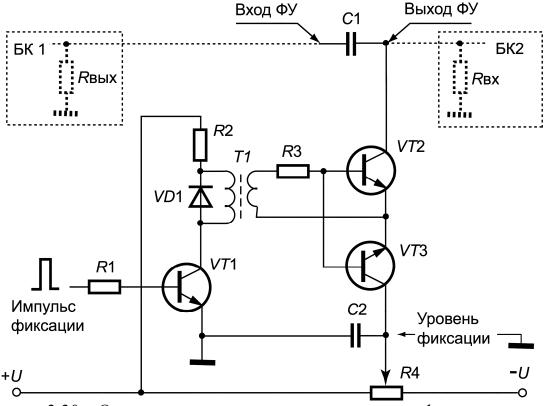

На рис. 1.24 показан один из вариантов построения балансной схемы аналогового ключа на двух биполярных транзисторах. По сравнению с вышерассмотренной схемой погрешности такого ключа могут быть снижены в 5–10 раз. К тому же в таком ключе обеспечена полная гальваническая развязка цепей управления и коммутации, благодаря использованию в цепи управления малогабаритного импульсного трансформатора.

Рисунок 1.24 – Пример балансной схемы аналогового ключа

В закрытом состоянии (если выполняется условие 1.23), токи, протекающие через транзисторы, направлены в противоположные стороны. Если коллекторные токи обоих транзисторов равны, то и результирующий ток, протекающий через источник сигнала и сопротивление нагрузки  $R_{\rm H}$ ,

равен нулю. Поскольку в открытом состоянии ТК остаточное напряжение  $U_{\kappa 9}$ , как это видно из положения линии отпирания (рис. 1.23б) не зависит от направления тока, протекающего через транзистор, то при идеальном подборе транзисторов остаточные напряжения  $U_c$  (напряжения в точке «c») компенсируют друг друга. Следовательно,  $U_{\text{вых}} \approx U_{\text{вх}}$ . Величину сопротивлений резисторов R1 и R2 следует выбирать исходя из требуемого тока базы и величины управляющего напряжения  $U_v$  в режиме насыщения.

Балансная схема, приведенная на рис. 1.24, может быть, например, рекомендована в составе узлов выборки-хранения, фиксаторов уровня и др.

В качестве примера ниже приводим параметры серийно выпускаемой российской промышленностью микросхемы балансного компенсированного аналогового ключа 162КТ1:

- сопротивление ключа в открытом состоянии  $R_{\text{отк}}$  ≈ 100 Ом;

- остаточное напряжение открытого ключа  $U_c < 300$  мкВ;

- ток закрытого ключа  $I_c < 50$  мкA;

- входное напряжение для обеспечения открытого состояния ключа  $U_{\rm Bx}$  < 30 B;

- сопротивление ключа в закрытом состоянии  $R_{3ak}$  ≈ 6·10<sup>5</sup> Ом;

- максимально допустимый ток базы  $I_{6 max} = 10$  мА;

- максимально допустимый ток коллектора  $I_{\kappa max} = 10 \text{ мA}$ .

#### 1.3.3 Особенности работы ключей на полевых транзисторах

Полевой транзистор в области малых напряжений сток-исток ведет себя как резистор, сопротивление которого может изменяться во много раз при изменении управляющего напряжения затвор-исток  $U_{\text{зи}}$ . Упрощенная схема последовательного ключа на полевом транзисторе с управляющим p-n переходом показана на рис. 1.25 а.

Рисунок 1.25— Схема ключа на полевом транзисторе с управляющим p-n переходом (a), на МОП-транзисторе (б)

Если управляющее напряжение  $U_{\rm y}$  установить меньшим, чем минимально возможное входное напряжение, транзистор закроется, и выходное напряжение станет равным нулю. Чтобы транзистор был открыт,

напряжение затвор-исток  $U_{3\mu}$  следует поддерживать равным нулю, обеспечивая тем самым минимальное сопротивление канала. Если же это напряжение станет больше нуля, управляющий p-n переход откроется, и выход коммутатора окажется соединенным с цепью управления. Однако равенство нулю  $U_{3\mu}$  реализовать непросто, поскольку потенциал истока изменяется в соответствии с изменением входного потенциала.

Проблемы подобного рода не возникают, когда роль ключа выполняет полевой транзистор с изолированным затвором (МОП-транзистор). Такой транзистор переводится в открытое состояние, когда управляющее напряжение  $U_{\rm v}$  большее, чем максимальное входное положительное напряжение. Важно заметить, что даже в таком случае ток затвора равен нулю. Схема ключа на МОП-транзисторе приведена на рис. 1.25б. В данной схеме ключом является n-канальный МОП-транзистор обогащенного типа [5]. При  $U_{34}$ <0 сопротивление канала достигает единиц или даже десятков ГОм. Подача на затвор значительного положительного напряжения относительно истока приводит канал в проводящее состояние с небольшим сопротивлением 20...200 Ом. Приведенная схема будет работать при положительных входных сигналах, которые, по крайней мере, на 5 В меньше, чем  $U_{v}$ . При более высоком уровне сигнала напряжение затвор-исток будет недостаточно, для удержания транзистора в открытом состоянии (сопротивление канала в открытом состоянии  $R_{\text{отк}}$  начнет расти); отрицательные входные сигналы вызовут включение транзистора при заземленном затворе. Поэтому, если надо переключать сигналы обеих полярностей (например, в диапазоне от -10 до +10 B), то можно использовать такую же схему, соединив подложку с источником –15 В и подавая на затвор напряжение +15 B (включено) или -15 B (выключено).

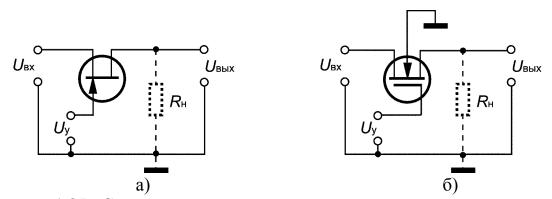

Лучшими характеристиками обладают ключи на комплементарных МОП-транзисторах (КМОП-ключи), показанные на рис. 1.26.

Рисунок 1.26 – Схема ключа на комплементарных МОП-транзисторах

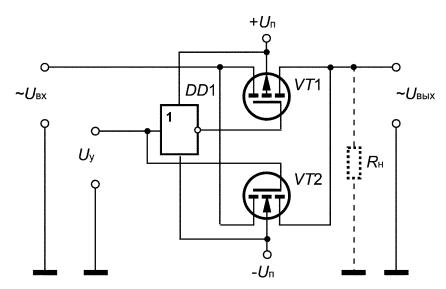

На подложку транзистора VT1 подается положительное питающее напряжение  $+U_{\rm n}$ , а на подложку транзистора VT2 – отрицательное питающее напряжение  $-U_{\Pi}$ . При высоком уровне управляющего сигнала напряжение на затворе n-канального транзистора VT2 практически равно  $+U_{\rm II}$ . В таком случае транзистор VT2 проводит сигналы с уровнями от  $-U_{\rm II}$  до  $+U_{\Pi}$  без нескольких вольт, хотя по мере приближения входного сигнала к верхнему пределу сопротивление  $R_{\text{отк}}$  растёт (зависимость сопротивления между стоком и истоком  $U_{cu}$  показана на рис. 1.27). В это время на затворе VT1напряжение, снимаемое выхода инвертора DD1, c противоположное значение, близкое к  $-U_{\rm n}$ . Транзистор VT1 пропускает сигналы с уровнями от  $+U_{\rm n}$  до значения, на несколько вольт выше  $-U_{\rm n}$ . Таким образом, все сигналы в диапазоне от  $-U_{\rm n}$  до  $+U_{\rm n}$  проходят через открытый ключ, который представляет собой двухполюсник с малым сопротивлением  $R_{\text{отк}}$  (рис. 1.17 в).

Рисунок 1.27 — Зависимость сопротивлений каналов КМОП-ключа от напряжения входного сигнала

При переключении управляющего сигнала на низкий уровень напряжение на затворе n-канального транзистора VT2 устанавливается близким к  $-U_{\Pi}$ , а напряжение на затворе p-канального транзистора VT1 устанавливается близким к  $+U_{\Pi}$ . Тогда при всех значениях входного сигнала в диапазоне от  $-U_{\Pi}$  до  $+U_{\Pi}$  оба транзистора заперты, и цепь коммутатора разомкнута. Эта схема работает в двух направлениях: любой ее зажим может служить входным. Она является основой практически для всех ИМС аналоговых коммутаторов, выпускаемых в настоящее время.

Хорошим приложением ключей на полевых транзисторах являются аналоговые мультиплексоры и демультиплексоры (см. раздел 2.6).

Ниже остановимся на некоторых недостатках, свойственных ключам на полевых транзисторах, которые в определенной степени ограничивают сферу их практического применения.

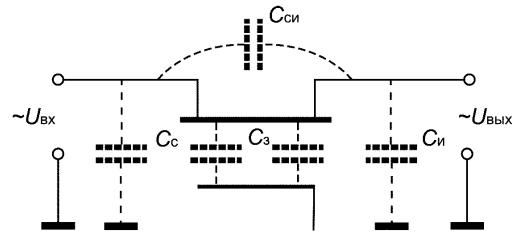

Реальные ключи на полевых транзисторах обладают заметными межэлектродными ёмкостями (рис. 1.28), которые оказывают влияние на динамические характеристики аналоговых коммутаторов и предопределяют требования к источнику входного сигнала.

Рисунок 1.28 – Межэлектродные ёмкости ключа на полевом транзисторе

Ёмкость между стоком и истоком  $C_{cu}$  фактически представляет собой паразитную ёмкость между входом и выходом. Наличие этой ёмкости является причиной прохождения сигнала через разомкнутый ключ. На низких частотах влияние этой ёмкости не вызывает проблем, однако поскольку ёмкостное сопротивление обратно пропорционально частоте, то влияние этой ёмкости особенно заметно на высоких частотах в спектре входного сигнала. Одним из эффективных методов уменьшения сквозного прохождения сигнала является использование пары последовательно включённых ключей (рис. 1.29 а) или ещё лучше использование схемы последовательно-параллельного коммутатора (рис. 1.29 б).

Рисунок 1.29 — Возможные методы уменьшения сквозного прохождения сигнала

Построение последовательно-параллельных коммутаторов наиболее просто реализуется при использовании специально выпускаемых интегральных микросхем, содержащие по два нормально замкнутых (т.е. замкнутых при низком уровне управляющего сигнала) и два нормально разомкнутых ключа (например, MAX314, DG414, 590КН4 и др.).

**Ёмкости стока**  $C_{\rm c}$  и истока  $C_{\rm h}$  относительно земли выполняют шунтирующее действие, которое приводит к спаду частотной характеристики в области высоких частот. Нежелательное влияние этих ёмкостей тем сильнее, чем больше выходное сопротивление источника входного сигнала и сопротивление замкнутого ключа. Совместно с этими сопротивлениями ёмкости  $C_{\rm c}$  и  $C_{\rm u}$  образуют фильтр нижних частот.

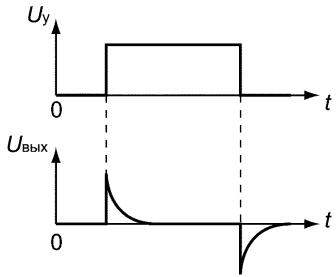

**Ёмкость затвор-канал**  $C_3$  распределена по всей длине канала. Её влияние проявляется во время перехода ключа в противоположное состояние, т.е. в период замыкания и размыкание ключа. Дело в том, что каждый скачок управляющего напряжения  $U_y$ , на затворе вызывает изменение заряда в цепи канала. В качестве примера на рис. 1.30 показана типичная форма сигнала, которая наблюдается на выходе n-канального ключа (рис. 13 б) при нулевом уровне входного сигнала и при нагрузке, которую можно представить сопротивлением 10 кОм с параллельно включённой ёмкостью 20 пФ.

Наблюдаемый паразитный сигнал вызван процессом переноса заряда в канале через ёмкость  $C_3$ , (примерно равную 5 пФ) при изменении  $U_y$ . Величина переносимого заряда  $q = \pm C_3 \cdot (U_{y+} - U_{y-})$ . Важно подчеркнуть, что величина переносимого заряда зависит от величины  $U_{y+} - U_{y-}$  и совершенно не зависит от времени переходного процесса. При более плавном изменении управляющего напряжения  $U_y$  наблюдается помеха меньшая по амплитуде, но большая по длительности (с такой же площадью под графиком).

Рисунок 1.30 — Управляющий сигнал  $U_{\rm y}$  и помеха, вызванная переносом заряда в канале

Частично эта помеха попадает на вход ключа и вызывает нежелательные переходные процессы в выходной цепи источника коммутируемого сигнала. Минимизировать влияние этой помехи можно, обеспечивая минимальное (близкое к нулю) выходное сопротивление источника коммутируемого сигнала, а также уменьшая сопротивление нагрузки (однако последнее связано с увеличением нагрузки на источник входного сигнала).

### 1.4 Фотоприёмный узел на основе пары фотодиод — операционный усилитель

При реализации быстродействующих оптико-электронных измерительных систем в качестве фотоприёмников до сих пор широко используются фотодиоды. С некоторой долей условности их можно отнести к фотоприёмникам «мгновенного» действия. При этом имеют в виду характерную для таких фотоприёмников зависимость выходного электрического сигнала (фототока) от текущих значений входного оптического сигнала (оптического потока), в отличие от фотоприёмников, работающих в режиме накопления, т.е. временного интегрирования энергии сигнала (например, ФПЗС, КМОП и др.).

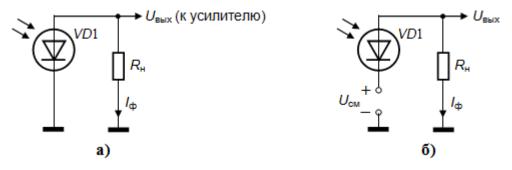

На рис. 1.31 показан классический способ включения фотодиода, который часто используется в оптико-электронных датчиках обнаружения оптического потока (оптические локаторы, импульсные дальномеры и др.). В таких случаях обычно не предъявляется серьёзных требований к линейности свет-сигнальной характеристики фотоприёмного узла по сравнению с требованиями достижения его максимальной обнаружительной способности.

Рисунок 1.31 – Схемы включения фотодиода в фотогальваническом (a) и диодном (б) режимах

Нагрузочный резистор  $R_{\rm H}$  (рис. 1.31) фактически играет роль преобразователя фототока  $I_{\rm \varphi}$  в напряжение выходного сигнала  $U_{\rm \varphi}$ :  $U_{\rm \varphi} = I_{\rm \varphi} \cdot R_{\rm H}$ . При этом увеличение величины сопротивления нагрузочного резистора, с одной стороны способствует увеличению чувствительности фотоприёмного

узла, а с другой приводит к увеличению нелинейности свет-сигнальной характеристики. Это объясняется тем, что при значительных величинах сопротивления нагрузки ( $R_{\rm H} > 10^4~{\rm OM}$ ) падение напряжения на фотодиоде существенно зависит величины фототока, и от падения напряжения на резисторе.

В задачах, так или иначе связанных с необходимостью измерения оптических сигналов, требование обеспечения линейности свет-сигнальной характеристики имеет большое значение, поскольку оно в значительной мере предопределяет метрологические параметры оптико-электронного прибора. В подобных случаях наиболее предпочтительным представляется другой способ реализации фотоприёмного узла, который заключается в сопряжении фотодиода с преобразователем ток-напряжение на операционном усилителе (рис. 1.32, см. также раздел 1.1).

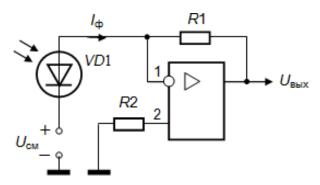

Рисунок 1.32 – Схема сопряжения фотодиода с преобразователем ток-напряжение

В данном примере фотодиод работает при запертом p-n переходе (диодный режим включения). Запирание p-n перехода обеспечивается с помощью напряжения смещения  $U_{\rm cm}$ . Напомним, что потенциал точки 1 ( $\phi$ 1) практически равен нулю (виртуальный нуль).

Фототок  $I_{\phi}$ , пропорциональный потоку оптического излучения, попадающего на фотодиод, образуют неосновные носители заряда, концентрация которых мала и, следовательно, внутреннее сопротивление фотодиода велико. Можно считать, что фототок, являющийся одновременно входным током преобразователя, замыкается через резистор обратной связи R1, поскольку входной ток собственно ОУ (ток через точки 1 и 2) пренебрежимо мал. Тогда с учётом того, что  $\phi 1 \approx 0$  можно записать

$U_{\text{вых}} \approx I_{\phi} \cdot R1 = \Phi_{\text{e}} \cdot S_{I'} R1 = \Phi_{\text{e}} \cdot S_{U},$  (1.32) где  $S_{I}$  — токовая чувствительность фотодиода [A/Bт];  $\Phi_{\text{e}}$  — поток оптического излучения [Bт], воздействующий на фоточувствительную площадку;  $S_{U} = S_{I'} R1$  — вольтовая чувствительность фотоприёмного узла.

Важно заметить, что при такой схеме включения фотодиод как бы «испытывает» очень малое сопротивление нагрузки, которым фактически

является входное сопротивление преобразователя ток-напряжение (см. раздел 1.1)

$$R_{\rm BX} \approx R1 / K_0. \tag{1.33}$$

При этом напряжение на *p-n* переходе практически не зависит от фототока, что при высокой вольтовой чувствительности позволяет добиться хорошей линейности свет-сигнальной характеристики фотоприёмного узла. К тому же, как видно из выражения (1.32), напряжение выходного сигнала практически не зависит ни от коэффициента ОУ, ни от напряжения питания, что способствует достижению высокой стабильности метрологических характеристик оптико-электронной измерительной системы.

Пусть, например,  $I_{\phi}=1$  мкА; R1=1 Мом;  $K_0=10^5$ . Тогда получим:  $U_{\text{вых}}=1$  В;  $R_{\text{вх}}=10$  Ом. Таким образом, достаточно высокую чувствительность фотоприёмного узла удаётся получить при хорошей линейности свет-сигнальной характеристики. Изменяя в широких пределах величину сопротивления резистора обратной связи R1, можно пропорционально изменять вольтовую чувствительность фотоприёмного узла. Это позволяет использовать данную схему в большом динамическом диапазоне  $\Phi_e$ .

Однако следует иметь в виду, что максимальное величина сопротивления в цепи обратной связи не должна превышать

$$R1 \leq U_{max \, {

m OV}}/(S_I \cdot \Phi_{e \, max}),$$

(1.34) где  $U_{max \, {

m OV}}$  — максимально допустимое напряжение на выходе ОУ, при котором сохраняется линейность усиления (даётся в справочнике);  $\Phi_{e \, max}$  — максимальная величина оптического потока в рабочем диапазоне.

Выбирая сопротивление резистора в цепи обратной связи, выполнение условия (1.34) является необходимым, но не всегда достаточным. Так при работе с очень малыми потоками, когда стремятся обеспечить максимально возможную чувствительность фотоприёмного узла, верхний предел величины сопротивления R1 следует помимо выражения (1.33) определять с учётом следующих обстоятельств.

При больших значениях сопротивления *R*1 (более 1 Мом) напряжение сигнала на выходе ОУ и входное сопротивление преобразователя ток-напряжение (являющееся фактически эквивалентным сопротивлением нагрузки фотодиода) должны определяться с помощью более точных выражений, учитывающих параметры реального ОУ

$$U_{\text{вых}} = \frac{\Phi_e S_I R 1}{1 + R 1 / (K_0 R_{\text{bx OY}}) + 1 / K_0}$$

(1.35)

$$R_{\rm bx} = \frac{R1}{1 + K_0 + R1/R_{\rm bx \, OY}} \tag{1.36}$$

Очевидно, что при  $R1/R_{\rm bx\,OY} << K_0$  выражения (1.34) и (1.35) приводятся к виду (1.32) и (1.33).

Продифференцировав выражение (1.35) по  $K_0$  и пренебрегая членами второго порядка малости, получим зависимость относительного изменения

сигнала на выходе фотоприёмного узла от нестабильности коэффициента усиления ОУ  $\Delta K_0$ .

$$\delta = \Delta U_{\text{BMX}} / U_{\text{BMX}} = (R1/R_{\text{BX OC}} + 1) \frac{\Delta K_0}{K_0}$$

(1.37)

С помощью последнего выражения, а также с учётом параметров реального ОУ  $K_0$ ,  $R_{\rm BX}$  ОУ можно при заданной предельной относительной погрешности измерения определить максимальное сопротивление R1 в цепи обратной связи в диапазоне рабочих температур фотоприёмного узла.

При работе с модулированным потоком оптического излучения следует учитывать зависимость входного сопротивления и коэффициента передачи преобразователя ток-напряжение от частоты. выражения (1.35) и (1.36) могут быть представлены в виде

$$\dot{U}_{\text{BMX}} = \frac{\Phi_e S_I Z 1}{1 + Z 1 / (\dot{K}_0 Z_{\text{BX OV}}) + 1 / \dot{K}_0}$$

(1.38)

$$\dot{U}_{\text{вых}} = \frac{\Phi_e S_I Z 1}{1 + Z 1 / (\dot{K}_0 Z_{\text{вх ОУ}}) + 1 / \dot{K}_0}$$

$$Z_{\text{вх}} = \frac{Z 1}{1 + \dot{K}_0 + Z 1 / Z_{\text{вх ОУ}}}$$

(1.38)

Здесь  $\dot{U}_{\text{вых}}$ , Z1,  $Z_{\text{вх ОС}}$ ,  $\dot{K}$  — соответственно выходное напряжение, сопротивление в цепи обратной связи, входное сопротивление и коэффициент усиления ОУ, записанные в комплексном виде.

$Z_{\mbox{\tiny RX OC}}$  и  $\dot{K}$  зависят от цепей коррекции частотной характеристики реального ОУ. Комплексное сопротивление в цепи обратной связи определяется следующим выражением

$$Z1 = R1/(1 - j \omega C_{\text{o.c.}}) \tag{1.40}$$

где  $C_{\text{o.c.}}$  – паразитная ёмкость монтажа в цепи обратной связи;  $\omega$  – угловая, частота в спектре сигнала;  $\omega = 2\pi f (f - \mu )$  циклическая частота,  $\Gamma \mu$ ).

Заметим, что при правильно выбранном ОУ, обладающим достаточным усилением в заданном диапазоне частот, наибольшее влияние на частотную характеристики фотоприёмного узла оказывает именно цепь обратной связи. При этом вольтовую чувствительность фотоприёмного узла можно представить как функцию частоты

$$S_U(f) \approx \frac{S_I R 1}{\sqrt{1 + (2\pi \cdot f \cdot R 1 \cdot C_{\text{o.c.}})^2}}$$

(1.41)

Последнее обстоятельство следует иметь в виду при выборе схемы, обеспечивающей возможность управления чувствительностью по цепи обратной связи. Необходимо принимать меры для уменьшения монтажной ёмкости  $C_{0,c}$  В этой связи хорошим решением может быть использование в цепи обратной связи фоторезисторного оптрона (см. раздел 3.4).

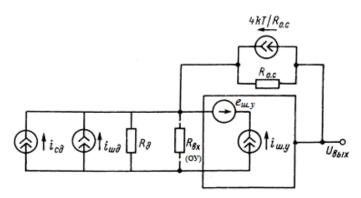

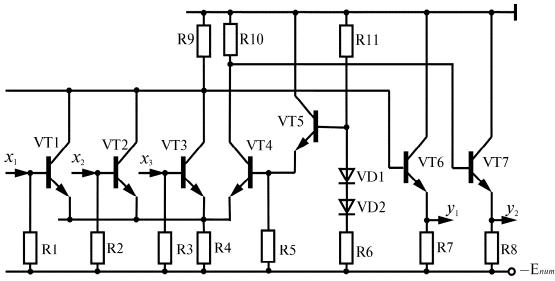

При работе в режиме малых оптических сигналов существенное значение приобретают шумовые характеристики рассматриваемого фотоприёмного узла. На рис. 1.33 показана эквивалентная схема пары фотодиод — операционный усилитель. Фотодиод можно рассматривать как источник тока сигнала  $i_{\text{с.д.}}$  и тока шума  $i_{\text{ш.д.}}$ , обладающий внутренним динамическим сопротивлением  $R_{\text{д.}}$ . Напряжение шума на выходе ОУ в полосе частот  $\Delta f = 1$   $\Gamma$ ц определяется выражением

$$U_{\text{III.BЫX}} = \sqrt{e_{\text{III.oy}}^2 + (i_{\text{III.oy}}^2 + i_{\text{III.op}}^2 + i_{R_{o.c.}}^2)R_{o.c.}^2} \quad [B/\Gamma \Pi^{1/2}], \tag{1.42}$$

где  $e_{\text{ш. оу}}$ ,  $i_{\text{ш. оу}}$ ,  $i_{\text{ш. фд}}$ ,  $i_{R \text{ о.c}}$ - спектральные плотности, напряжения шума ОУ, шумового тока ОУ, шумового тока фотодиода и шумового тока резистора в цепи обратной связи соответственно.

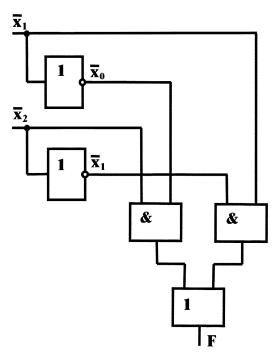

Рисунок 1.33 — Эквивалентная схема фотоприёмного узла на основе пары фотодиод — операционный усилитель

Шумовые параметры ОУ даются в справочнике. Например, для большинства современных отечественных ОУ спектральные плотности шумового напряжения и шумового тока находятся соответственно в следующих пределах:  $e_{\text{ш. оу}} = (1 \dots 7) \cdot 10^{-8} \text{ B/Г ц}^{1/2}$ ;  $i_{\text{ш. оу}} = (1 \dots 2) \cdot 10^{-14} \text{ A/Г ц}^{1/2}$ . Плотность шумового тока фотодиода, работающего в диодном режиме,  $i_{\text{ш. фд}} = \sqrt{2eI_{\text{T}}}$ . Плотность шумового тока фотодиода, работающего в фотогальваническом режиме,  $i_{\text{ш. фд}} = \sqrt{4kT/R_{\text{д}}}$ . Плотность шумового тока резистора в цепи обратной связи (R1 на рис. 1.32),  $i_{R_{o.c.}} = \sqrt{4kT/R_{o.c.}}$ . Здесь  $I_{\text{T}}$  — темновой ток фотодиода; k — постоянная Больцмана; T — абсолютная температура p-n перехода.

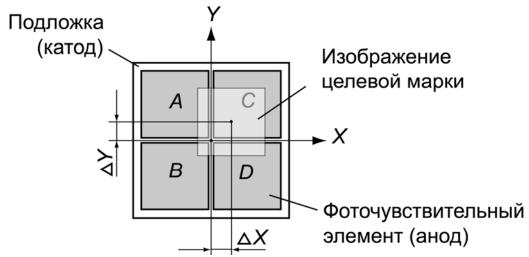

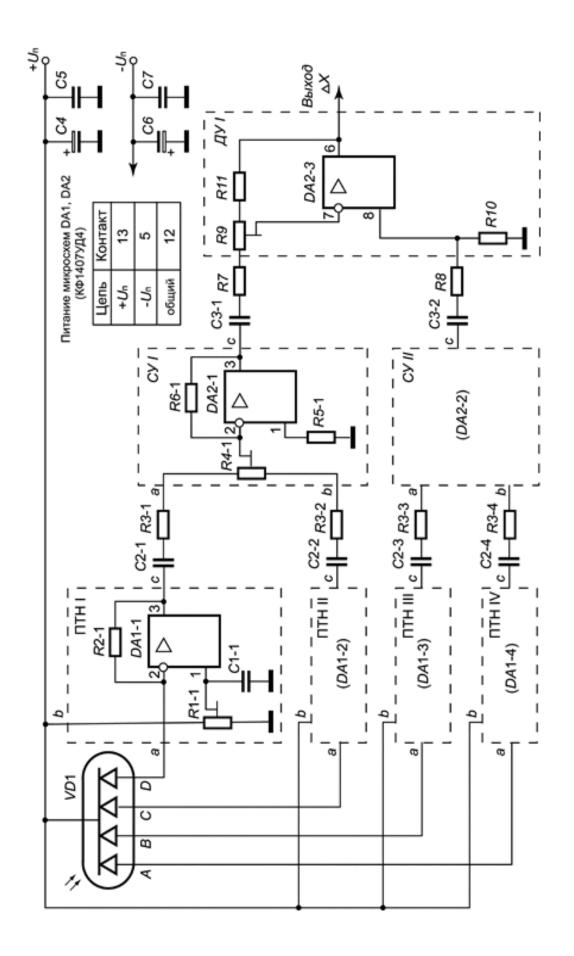

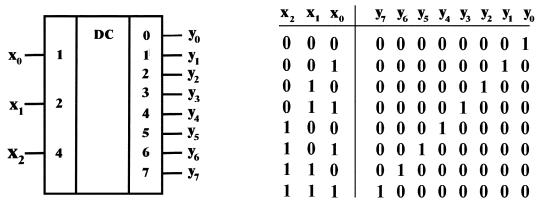

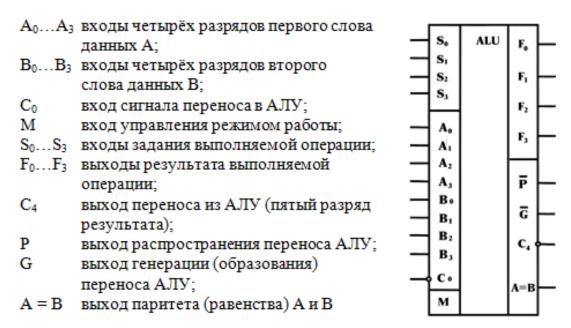

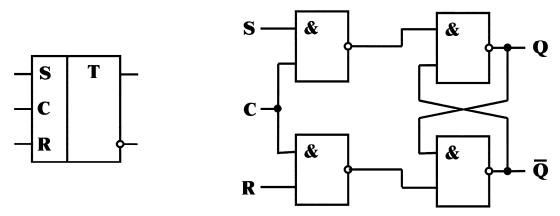

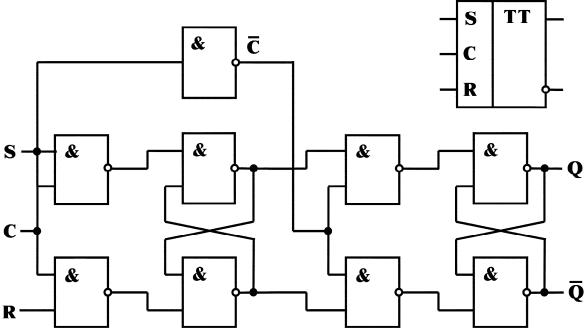

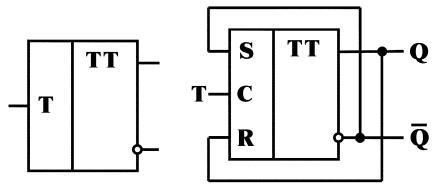

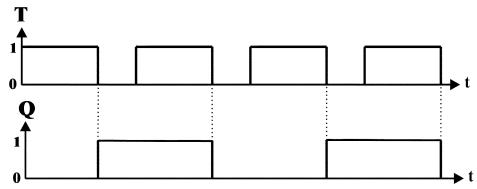

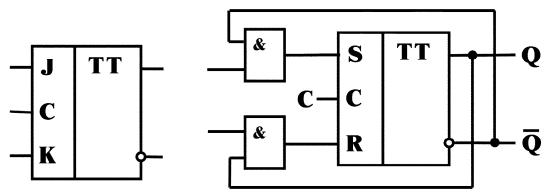

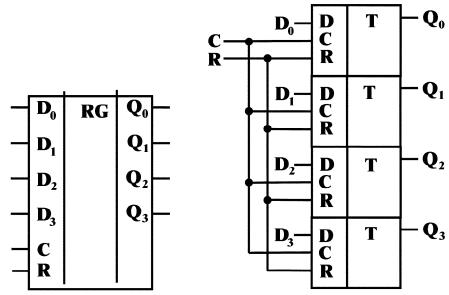

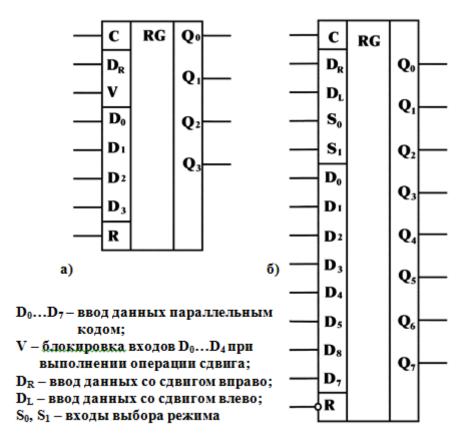

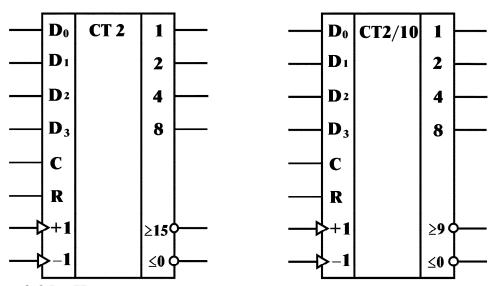

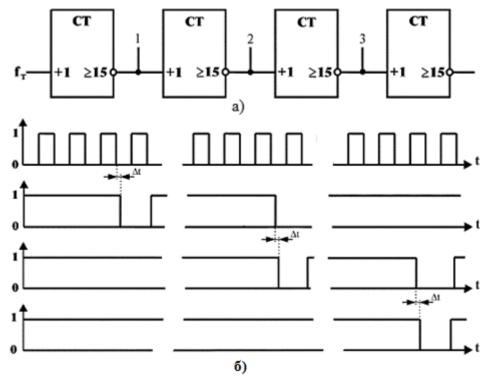

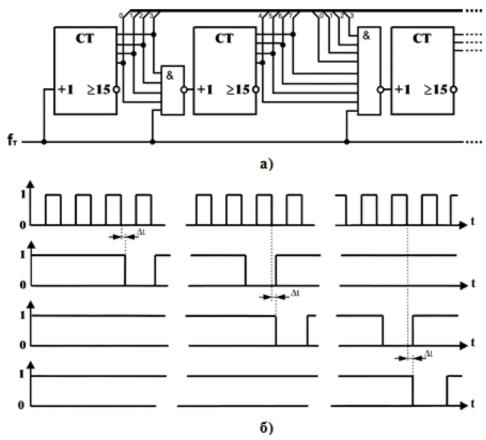

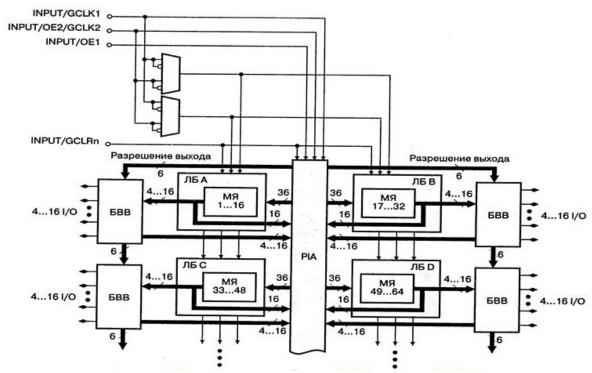

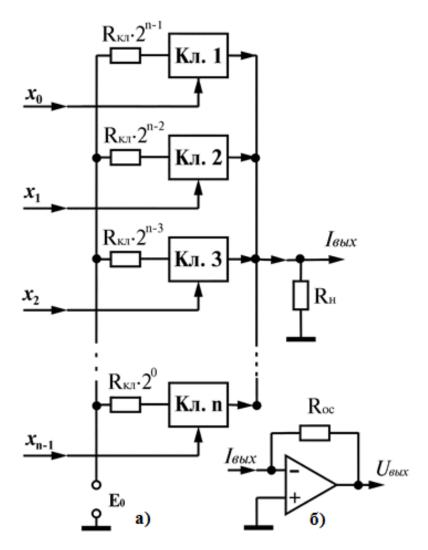

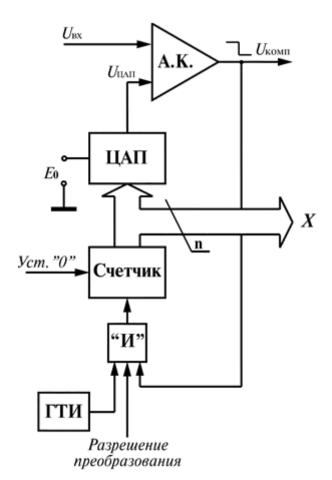

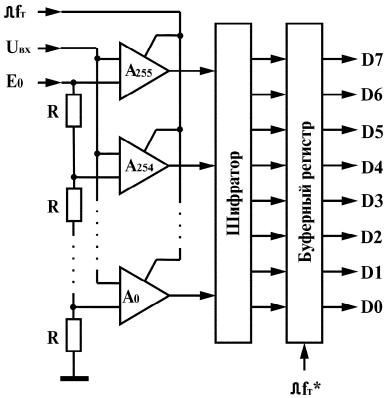

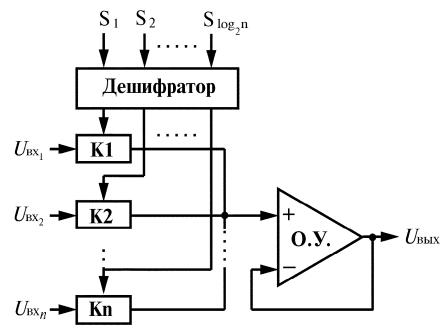

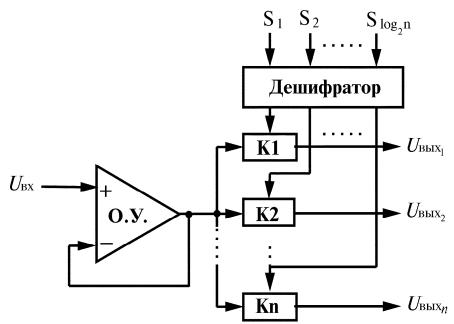

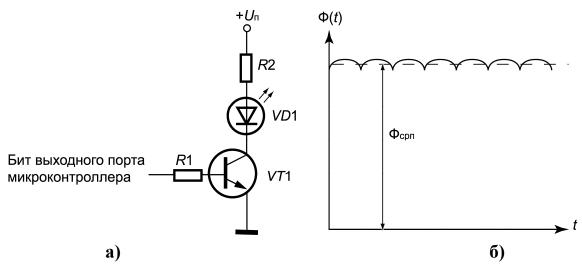

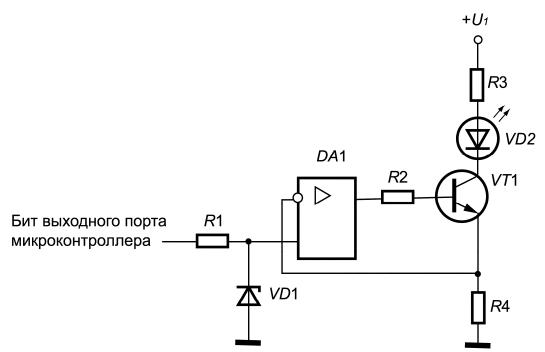

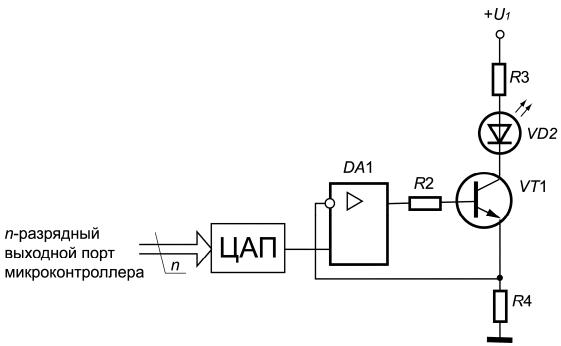

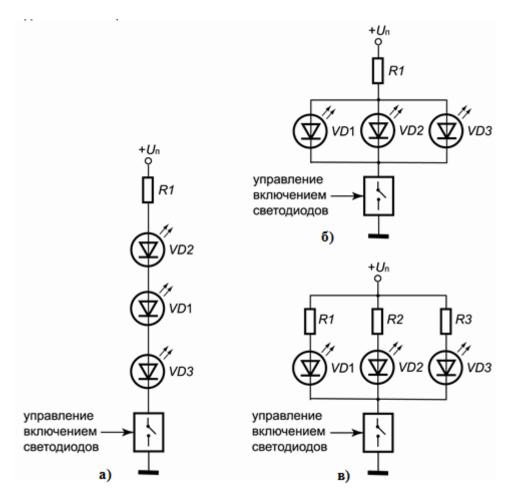

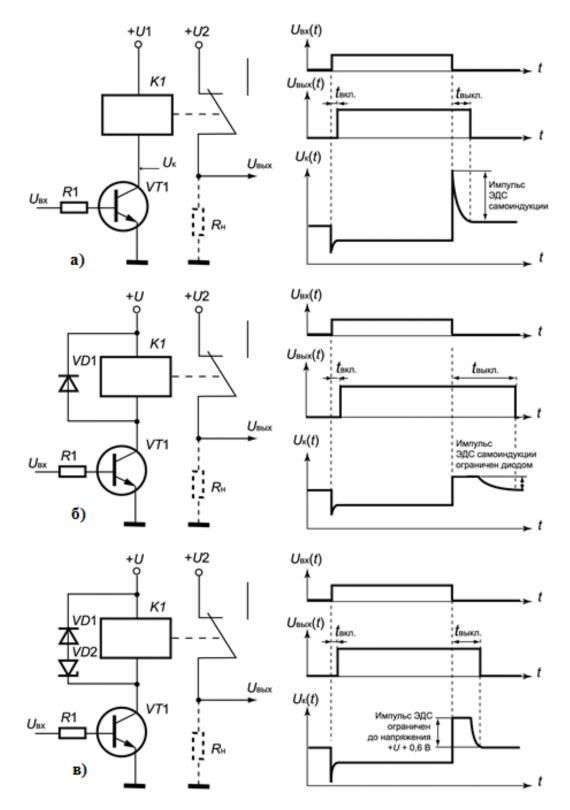

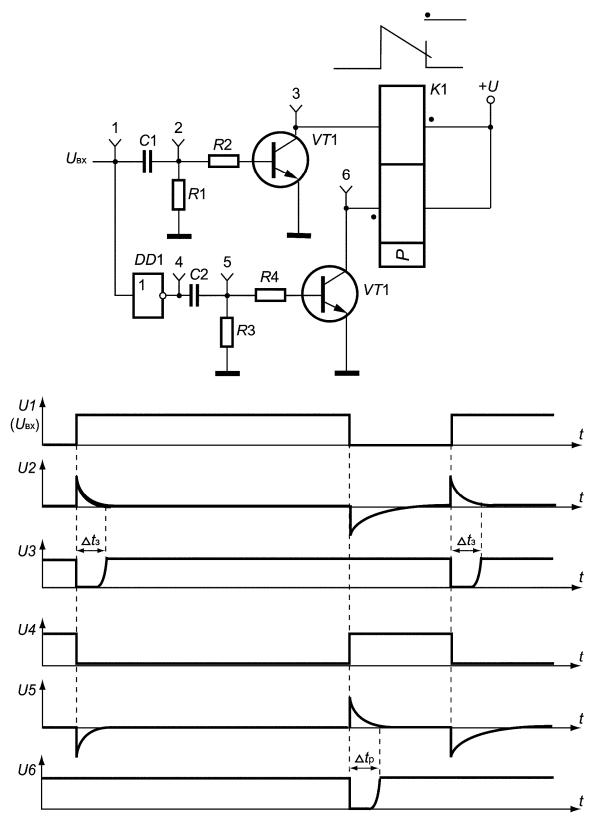

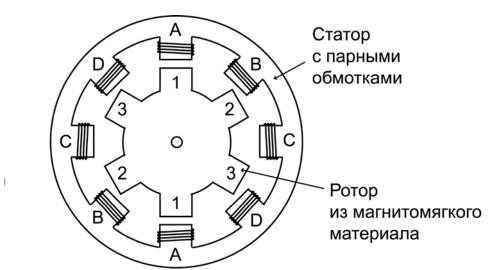

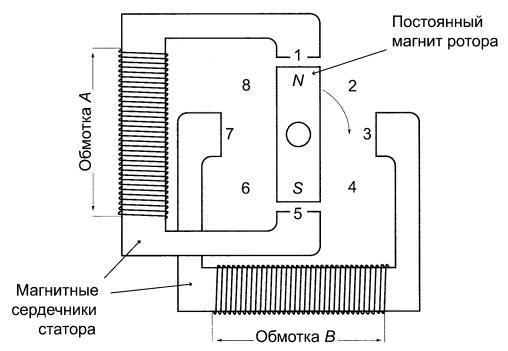

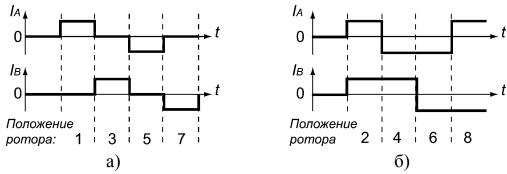

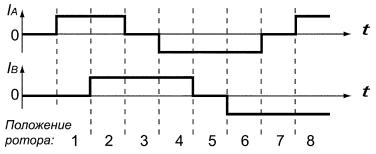

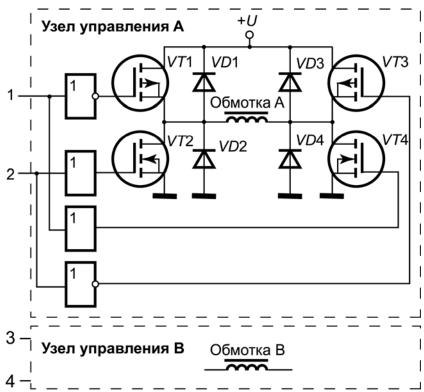

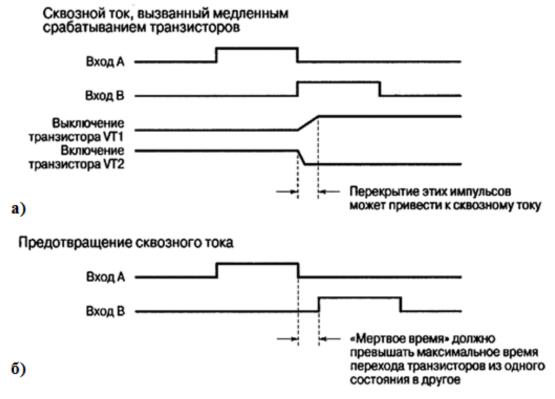

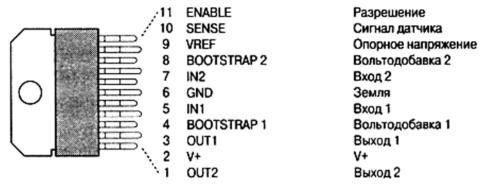

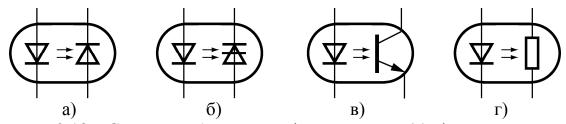

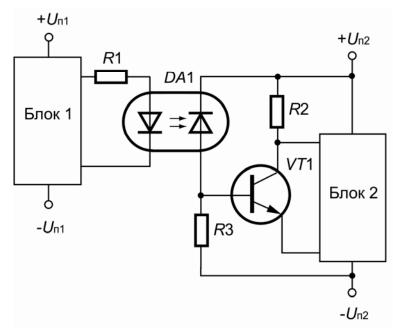

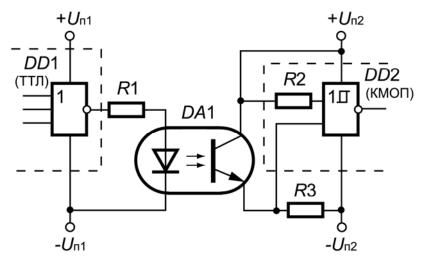

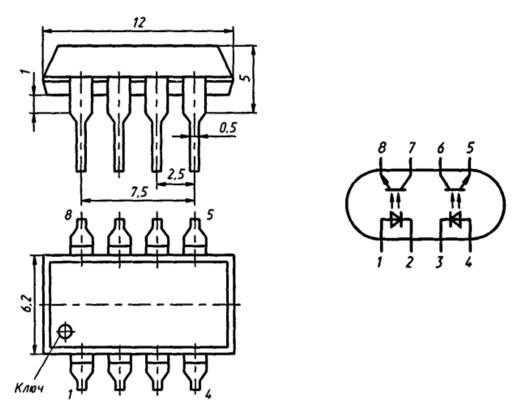

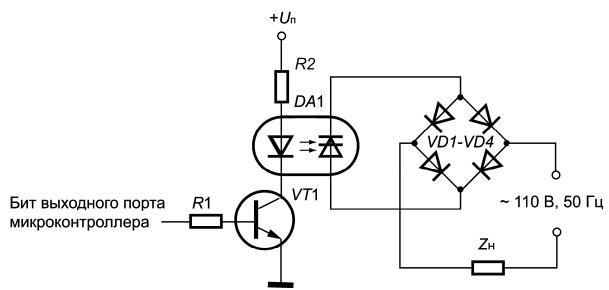

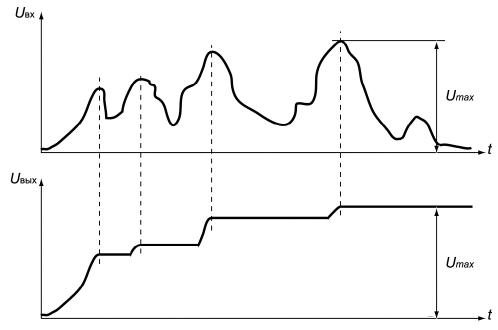

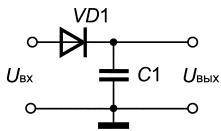

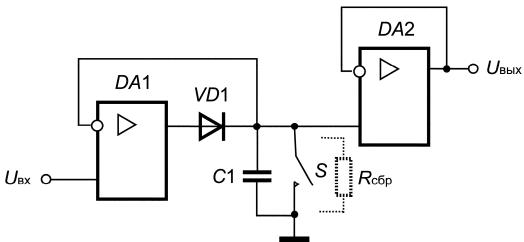

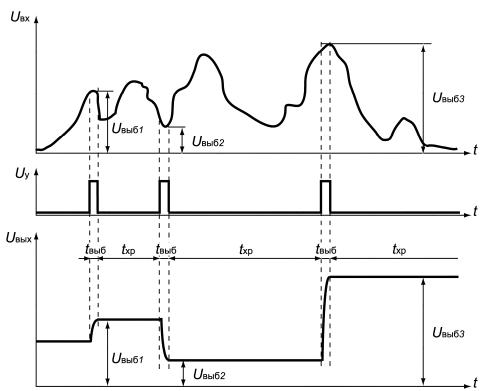

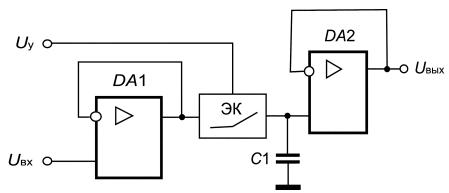

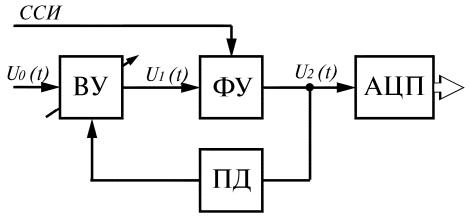

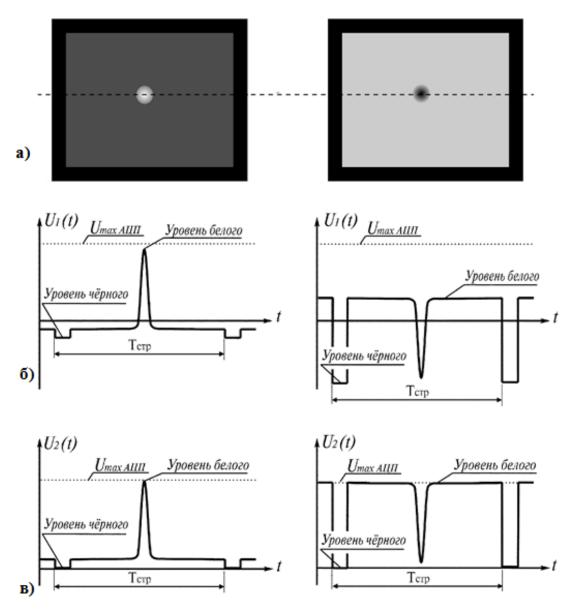

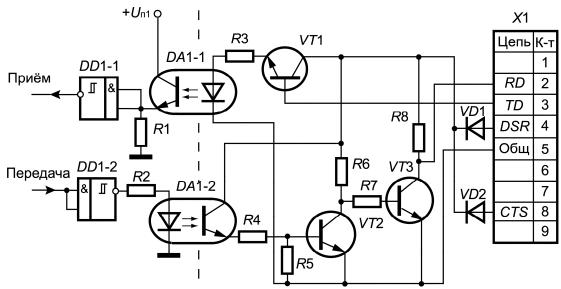

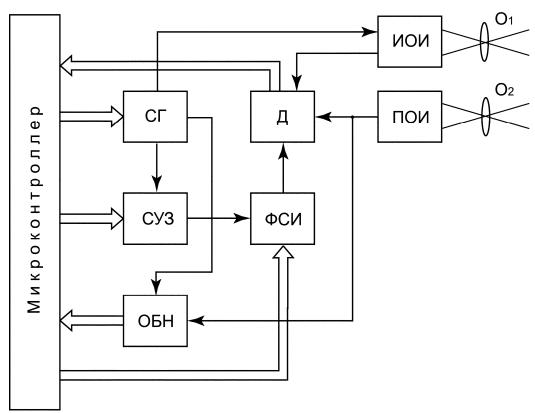

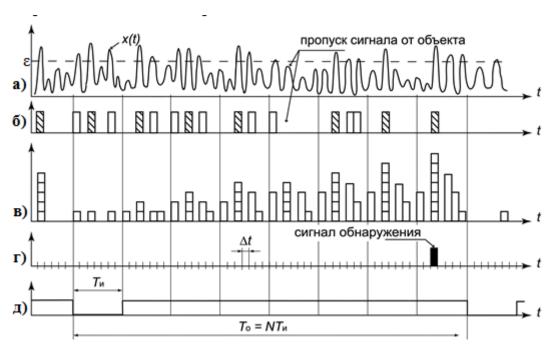

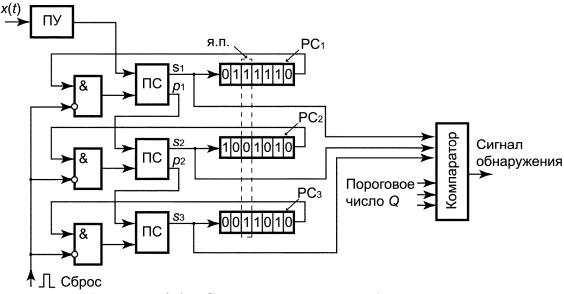

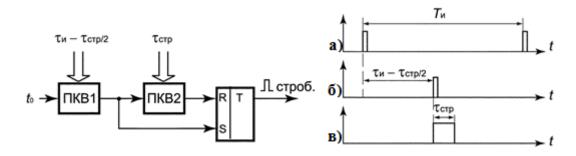

При использовании малошумящих ОУ преобладающую роль играют шумы фотодиода и шумы резистора в цепи обратной связи. Поэтому выражение (1.42) можно упростить