ITMO UNIVERSITY

## D.B. Afanasev, I.A. Bessmertny, S.V. Bykovskii, A.G. Ilina, S.V. Klimenkov, J.A. Koroleva

# Basic Computer Study guide Part 1

Saint Petersburg 2020

#### MINISTRY OF SCIENCE AND HIGHER EDUCATION OF THE RUSSIAN FEDERATION ITMO UNIVERSITY

## D.B. Afanasev, I.A. Bessmertny, S.V. Bykovskii, A.G. Ilina, S.V. Klimenkov, J.A. Koroleva

## Basic Computer Study guide Part 1

## **RECOMMENDED AS A STUDY GUIDE**

09.03.01 «Informatics and Computer Engineering» ITMO University and Hangzhou Dianzi University joint Bachelor's program «Computer Science and Technology»

Saint Petersburg 2020

D.B. Afanasev, I.A. Bessmertny, S.V. Bykovskii, A.G. Ilina, S.V. Klimenkov, J.A. Koroleva. Basic Computer study guide. Part 1 – Saint Petersburg: ITMO University, 2020. - 112 p.

Reviewer: Polyakov V.I., associate professor, Faculty of Software Engineering and Computer Systems, ITMO University.

The study guide contains theoretical and practical materials to conduct a laboratory work on «Computer Basics». It covers such topics as computer architecture, data representation in computers, processor instruction formats, principles of low-level program execution, concepts of program flow, subprograms and machine cycles.

The study guide explains how a computer executes programs and how it handles data. For practice the students are offered to use a simplified Basic Computer Model, which was designed at ITMO and successfully tested by generations of students. The model allows rapid development of skills to interact with internal features of computers, such as registers, internal memory, control and arithmetic units. It helps to create knowledge background to study more complex concepts in programming and computer architecture.

The study guide is for foreign computer science students of 09.03.01 «Informatics and Computer Engineering» of ITMO University and Hangzhou Dianzi University joint bachelor's program «Computer Science and Technology».

**ITMO University** - is the leading Russian university in the field of information and photonic technologies, one of the Russian universities with the status of the national research university granted in 2009. Since 2013 ITMO University has been a participant of the Russian universities' competitiveness raising program among the world's leading academic centers known as "5 to 100".

© ITMO University, 2020 © D.B. Afanasev, I.A. Bessmertny, S.V. Bykovskii, A.G. Ilina, S.V. Klimenkov, J.A. Koroleva 2020

## Contents

| Glossary                                                   | 4   |

|------------------------------------------------------------|-----|

| Introduction                                               | 9   |

| 1. The Basic Computer model                                | 10  |

| 1.1 Purpose and description of the Basic Computer model    | 10  |

| 1.2 Basic Computer instructions                            | 11  |

| 1.3 Representation of integers in Basic Computer           | 12  |

| 1.4 Arithmetic operations                                  | 15  |

| 1.5 Shifts and logical operations                          | 15  |

| 1.6 Computational process control                          | 16  |

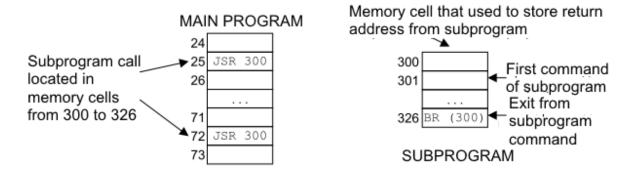

| 1.7 Subprograms                                            | 19  |

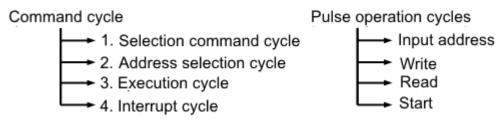

| 1.8 Machine instruction execution                          | 20  |

| 2. Laboratory works                                        | 24  |

| 2.1 Laboratory work 1. Program execution in Basic Computer | 24  |

| 2.1.1 Overview                                             | 24  |

| 2.1.2 Lab work task                                        | 24  |

| 2.1.3 Lab work guidance                                    | 25  |

| 2.1.4 Lab work variants                                    | 35  |

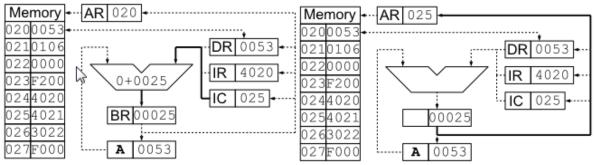

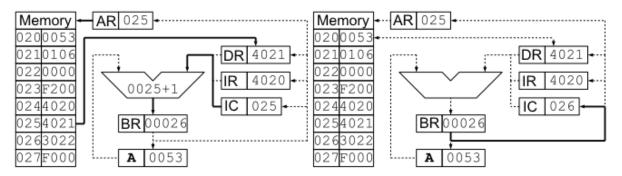

| 2.2 Laboratory work 2. Low level instruction execution     | 40  |

| 2.2.1 Overview                                             | 40  |

| 2.2.2 Lab work task                                        | 40  |

| 2.2.3 Lab work guidance                                    | 41  |

| 2.2.4 Lab work variants                                    | 55  |

| 2.3 Laboratory work 3. Program control flow                | 60  |

| 2.3.1 Overview                                             | 60  |

| 2.3.2 Lab work task                                        | 60  |

| 2.3.3 Lab work guidance                                    | 60  |

| 2.3.4 Lab work variants                                    | 74  |

| 2.4 Laboratory work 4. Subprograms                         | 84  |

| 2.4.1 Overview                                             | 84  |

| 2.4.2 Lab work task                                        | 84  |

| 2.4.3 Lab work guidance                                    | 85  |

| 2.4.4 Lab work variants                                    | 99  |

| Appendix A. Instruction Set of Basic Computer              | 109 |

| Appendix B. Basic Computer Hot Keys                        | 110 |

## Glossary

## A

| Abacus                                                                            | a simple mechanical device that was used to perform arithmetical operations in the ancient Near East, Europe, China, and Russia.                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access time                                                                       | a time period that is needed to reach a resource like a memory, a computer etc.                                                                                                                                                                                                                                                                                                        |

| Accumulator                                                                       | a register used by the processor to store results of arithmetic and logic operations from ALU.                                                                                                                                                                                                                                                                                         |

| Addition<br>Address bus                                                           | adding numbers or amounts together.<br>signal lines (wires) that are used in a computer to transfer the<br>address value to the memory or to peripheral devices to define a<br>place of data reading and writing.                                                                                                                                                                      |

| Address register<br>ALU<br>Analog computation<br>Analog computer<br>Analog signal | a register that holds the address value.<br>Arithmetic and Logic Unit. It is a part of the processor.<br>a kind of computation with data in analog representation.<br>a computer which works with analog signals.<br>a continuous signal.                                                                                                                                              |

| Arithmetic operation<br>Arithmometer<br>Application<br>Assembler                  | an operation with numbers or amounts such as addition,<br>subtraction, multiplication and division.<br>the first digital mechanical calculator.<br>a computer program that runs on a computer.<br>a computer program that converts a mnemonic program code to a<br>machine code. Assembler is also a language that is used to write<br>a mnemonic program code.                        |

| Assembly operation                                                                | an operation that represents a mnemonic code in a machine code.                                                                                                                                                                                                                                                                                                                        |

| В                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                        |

| Bit                                                                               |                                                                                                                                                                                                                                                                                                                                                                                        |

| Bit rate<br>Binary system                                                         | a minimal unit to represent information in digital computers.<br>how many bits per second can be transmitted using predefined<br>channels.<br>a system that uses only two symbols (0 and 1) to represent data.                                                                                                                                                                         |

| Bit rate                                                                          | how many bits per second can be transmitted using predefined channels.                                                                                                                                                                                                                                                                                                                 |

| Bit rate<br>Binary system                                                         | how many bits per second can be transmitted using predefined<br>channels.<br>a system that uses only two symbols (0 and 1) to represent data.                                                                                                                                                                                                                                          |

| Bit rate<br>Binary system<br>Binary number<br>Branch (in program)                 | <ul><li>how many bits per second can be transmitted using predefined channels.</li><li>a system that uses only two symbols (0 and 1) to represent data.</li><li>a number in the binary system.</li><li>a point in a computer program, where the algorithm can be changed depending on a condition.</li><li>a unit that is used to measure the amount of digital information.</li></ul> |

| Bit rate<br>Binary system<br>Binary number<br>Branch (in program)<br>Byte         | <ul><li>how many bits per second can be transmitted using predefined channels.</li><li>a system that uses only two symbols (0 and 1) to represent data.</li><li>a number in the binary system.</li><li>a point in a computer program, where the algorithm can be changed depending on a condition.</li><li>a unit that is used to measure the amount of digital information.</li></ul> |

| Compiler              | a computer program translating program commands which are<br>written in a programming language into sets of machine codes.                                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Complement code       | a code that is used to represent negative numbers.                                                                                                                                                                                                                                         |

| Computer              | a machine that can handle data and perform calculations<br>automatically according to the predefined program.                                                                                                                                                                              |

| Computer architecture | a set of rules and methods that describe the functionality, organization, and implementation of computer systems.                                                                                                                                                                          |

| Computer basics       | basic (fundamental) knowledge about the way a computer works.                                                                                                                                                                                                                              |

| Clock signal          | a signal that defines the time in a computer.                                                                                                                                                                                                                                              |

| Computer data         | data which a computer operates with. They could be numbers, symbols, and computer commands.                                                                                                                                                                                                |

| Computer memory       | a device that stores data.                                                                                                                                                                                                                                                                 |

| Control bus           | signal lines (wires) that are used in a computer to transfer control signals (like read/write signals) between its units such as ALU, the memory, registers etc.                                                                                                                           |

| Control flow          | the order in which program instructions or function calls are executed.                                                                                                                                                                                                                    |

| Control path          | a scheme of control signals transmission between functional units<br>such as ALU, the memory, registers etc.                                                                                                                                                                               |

| CPU                   | Central Processing Unit.                                                                                                                                                                                                                                                                   |

| Cyclic shift          | the operation of moving bits in a register. In the left cyclic shift,<br>the last bit goes to the place of the first bit, i.e. the bits go to the<br>left. In the right cyclic shift, the bits go to the right (another<br>direction) and the first bit goes to the place of the last bit. |

### D

| Data bus              | signal lines (wires) that are used in a computer to transfer data between its units such as ALU, the memory, registers etc. |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Data register         | a register in a processor that stores data.                                                                                 |

| Data representation   | a format of data storing or exchanging.                                                                                     |

| Data storage          | a storage for data, for example, a hard disk.                                                                               |

| Datapath              | a scheme of data signals transmission between functional units                                                              |

|                       | such as ALU, the memory, registers etc.                                                                                     |

| Data word             | a byte of data equals to eight bits.                                                                                        |

| Digital computer      | a computer in which data are represented as digital signals.                                                                |

| Digital design        | designing, developing and debugging electronic schemes using                                                                |

|                       | logic gates. Circuit design                                                                                                 |

| Digital signal        | a signal that uses data represented as a sequence of discrete                                                               |

|                       | values.                                                                                                                     |

| Distributed computing | a field of computer science that studies computer performance                                                               |

|                       | improvement and scalability using calculation on several                                                                    |

|                       | computers which are located in different places.                                                                            |

| Display               | an output device for representing graphical information.                                                                    |

| Discretization        | measuring values in discrete time moments and storing them as a                                                             |

|                       | sequence of discrete numbers.                                                                                               |

| Division              | an arithmetic operation that shows how many times a number is                                                               |

|                       | contained in a larger number.                                                                                               |

|                       |                                                                                                                             |

| Fan or cooler                                                                                                                                                                                   | a device for producing airflow, often for cooling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File system                                                                                                                                                                                     | a system or a computer program that defines and controls how                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ,                                                                                                                                                                                               | data is stored and fetched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Firmware                                                                                                                                                                                        | a class of computer programs that provides low-level control for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                 | computer hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fixed point numbers                                                                                                                                                                             | a real data type for a number that has a fixed number of digits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| F                                                                                                                                                                                               | after the decimal point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Float point numbers                                                                                                                                                                             | a real data type for a number that has a float position of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I                                                                                                                                                                                               | decimal point. This position is indicated as the exponent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                 | component.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Gate                                                                                                                                                                                            | a circuit part which controls outputs and inputs according to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                 | truth table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Н                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Hard disk                                                                                                                                                                                       | an electro-mechanical data storage device that uses magnetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                 | storage to maintain and retrieve digital information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hardware                                                                                                                                                                                        | physical parts of a computer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Hexadecimal (hex)                                                                                                                                                                               | a system that uses the hexadecimal format (sixteen symbols: 0, 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| numbers                                                                                                                                                                                         | 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F) to represent data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Human-machine                                                                                                                                                                                   | an interface that is used to communicate between humans and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| interface (HMI)                                                                                                                                                                                 | computers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                 | compaters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Ι                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Instruction set                                                                                                                                                                                 | a set of instructions that a processor can execute.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Instruction set<br>Integrated circuit                                                                                                                                                           | a set of instructions that a processor can execute.<br>a set of electronic circuits on one small piece of semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                 | a set of electronic circuits on one small piece of semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Integrated circuit                                                                                                                                                                              | a set of electronic circuits on one small piece of semiconductor material.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Integrated circuit<br>Instruction pointer                                                                                                                                                       | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Integrated circuit                                                                                                                                                                              | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Integrated circuit<br>Instruction pointer                                                                                                                                                       | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is</li></ul>                                                                                                                                                                                                                                                                                                                                                            |

| Integrated circuit<br>Instruction pointer<br>Instruction register                                                                                                                               | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li></ul>                                                                                                                                                                                                                                                                                                                                            |

| Integrated circuit<br>Instruction pointer<br>Instruction register                                                                                                                               | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li></ul>                                                                                                                                                                                                                                                                                                                                            |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System                                                                                                                 | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li></ul>                                                                                                                                                                                                                                                                                                                                            |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System                                                                                                                 | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li></ul>                                                                                                                                                                                                                                                                                                                                            |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L                                                                                                            | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li><li>an input/output system of a computer.</li></ul>                                                                                                                                                                                                                                                                                              |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital                                                                                      | <ul><li>a set of electronic circuits on one small piece of semiconductor material.</li><li>a processor register that stores the address of the next instruction to execute.</li><li>a processor register that stores the value of instruction that is being executed.</li><li>an input/output system of a computer.</li></ul>                                                                                                                                                                                                                                                                                              |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)                                                                  | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul>                                                                                                                                                                                                                                                                                         |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)                                                                  | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul>                                                                                                                                                                                                                                                                                         |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M                                        | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul>                                                                                                                                                                                                                                                                                         |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation                                             | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul>                                                                                                                                                                                          |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M<br>Machine code                        | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul> data and instruction representation that can be handled by a computer (machine).                                                                                                         |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M<br>Machine code<br>Mainframe           | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul> data and instruction representation that can be handled by a computer (machine). <ul> <li>big computers to process large amounts of data.</li> </ul>                                     |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M<br>Machine code<br>Mainframe<br>Memory | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul> data and instruction representation that can be handled by a computer (machine). <ul> <li>big computers to process large amounts of data.</li> <li>a device for storing data.</li> </ul> |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M<br>Machine code<br>Mainframe           | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul> data and instruction representation that can be handled by a computer (machine). <ul> <li>big computers to process large amounts of data.</li> </ul>                                     |

| Integrated circuit<br>Instruction pointer<br>Instruction register<br>I/O System<br>L<br>Layout (in digital<br>circuits design)<br>Logical operation<br>M<br>Machine code<br>Mainframe<br>Memory | <ul> <li>a set of electronic circuits on one small piece of semiconductor material.</li> <li>a processor register that stores the address of the next instruction to execute.</li> <li>a processor register that stores the value of instruction that is being executed.</li> <li>an input/output system of a computer.</li> </ul> an arrangement of elements in digital circuits. <ul> <li>a boolean logic operation.</li> </ul> data and instruction representation that can be handled by a computer (machine). <ul> <li>big computers to process large amounts of data.</li> <li>a device for storing data.</li> </ul> |

| Mnemonic code                      | a program code which represents every machine operation<br>(instruction) in a readable format for the user. For example,<br>mnemonic ADD stands for addition.                                |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Motherboard                        | the main printed circuit board found in general purpose<br>computers. It holds CPU and the memory allowing<br>communication between them, and provides connectors for<br>peripheral devices. |

| Multiprogramming                   | a feature that enables to run several programs simultaneously.                                                                                                                               |

| Multiplication                     | an arithmetic operation of adding a number to itself a particular number of times.                                                                                                           |

| Ν                                  |                                                                                                                                                                                              |

| Natural language interface         | a type of computer human interface where verbs, phrases and<br>clauses act as control commands for creating and modifying<br>data in computers.                                              |

| Negative numbers<br>Numbers range  | a real number that is less than zero.<br>a set of numbers.                                                                                                                                   |

| Р                                  |                                                                                                                                                                                              |

| Performance                        | an amount of instructions that a computer performs in a unit time.                                                                                                                           |

| PC                                 | personal computer.                                                                                                                                                                           |

| Parallel data transfer             | transfer of several data bits simultaneously.                                                                                                                                                |

| Personal computer                  | a multi-purpose computer with the size,<br>capabilities, and price feasible for an individual user.                                                                                          |

| Pipeline                           | a technique for implementing instruction-level parallelism within a single processor.                                                                                                        |

| Pop (memory operation)<br>Printing | fetching data from a predefined place.<br>a way to have a hardcopy of data stored in a computer which<br>are computing results. It is a way to transfer data outside the<br>computer.        |

| Processor                          | a part of a computer that executes program.                                                                                                                                                  |

| Processor instruction              | a command of a processor to do some manipulations with data.                                                                                                                                 |

| Program                            | a sequence of instructions that make a computer perform an action or a particular type of work                                                                                               |

| Program model of                   | a representation of a computer from a programmer's point of                                                                                                                                  |

| processor                          | view.                                                                                                                                                                                        |

| Programmer                         | a person who writes programs.                                                                                                                                                                |

| Programming                        | a process of creating a program.                                                                                                                                                             |

| Programming language               | a language that is used for writing a program.                                                                                                                                               |

| Push (memory operation)            | storing data to a predefined place.                                                                                                                                                          |

| P                                  |                                                                                                                                                                                              |

## R

| Register | a memory element that stores one word of data. |

|----------|------------------------------------------------|

| RISC     | Reduced Instruction Set Computer               |

| ROM      | Read Only Memory                               |

| 6      |   |

|--------|---|

| 1      |   |

| $\sim$ | · |

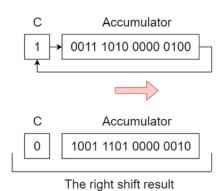

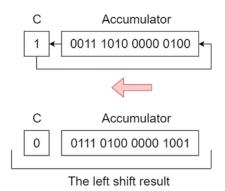

| Sequential data transfer<br>Shift | bit by bit data transfer.<br>an operation of moving bits in one direction inside the                                                                                                                    |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                            | register.<br>an electrical signal – a time-varying physical value (for<br>example, electric current, voltage, etc.) that contains<br>information.                                                       |

| Stack (memory)                    | a kind of memory that is based on the principle of last-in-first-<br>out pattern.                                                                                                                       |

| Software                          | a program or set of programs that tell the computer how to work.                                                                                                                                        |

| Subtraction                       | an arithmetical operation of taking a number or an amount from another number or an amount.                                                                                                             |

| Super-computer                    | a computer with a high level of performance.                                                                                                                                                            |

| System bus                        | signal lines (wires) that are used to connect CPU and the memory.                                                                                                                                       |

| Τ                                 |                                                                                                                                                                                                         |

| Terminal<br>Transistor            | a set of primary input and output devices for a computer<br>a semiconductor device used to amplify or switch electronic<br>signals and electrical power. It is a base of modern integrated<br>circuits. |

| Trigger                           | a device that can be in one stable state in every moment of<br>time. If an event occurs, it changes its state. It can store one<br>bit of data.                                                         |

| Truth table                       | a table that shows the dependence between input and output values in digital circuits.                                                                                                                  |

| U                                 |                                                                                                                                                                                                         |

| User i | nterface |

|--------|----------|

|--------|----------|

space where humans and machines communicate.

## Introduction

This study guide discusses the basic concepts of computer organization and functioning. The study guide is divided into two chapters.

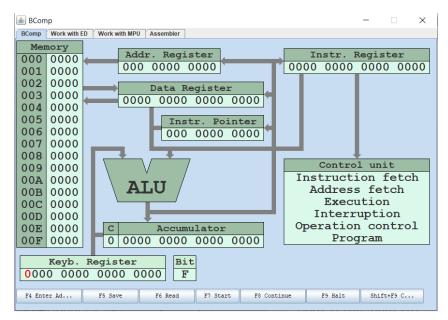

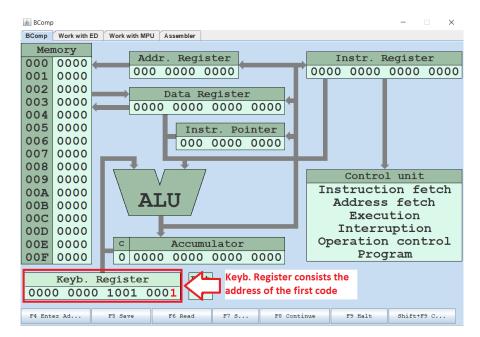

The first part provides information about data representation in a computer, how a computer executes program on a low level, the theory about the basic computer architecture, instruction formats and how a computer performs operations. The basic concepts are explained using the Basic Computer Model developed at ITMO University. This is a simplified model that has typical features of the widely used digital computers.

The second chapter contents a set of laboratory works that can be used to build up knowledge and develop skills of understanding a program execution process using the Basic Computer Model. Each laboratory work contents the step-by-step guides that help to successfully complete the task.

The assignments for the laboratory works cover such topics as:

- basic principles of program execution in computer;

- low level instruction execution;

- program control flow;

- subprograms.

To work with the book the students need:

- The Basic Computer Model that can be downloaded by this link: <u>https://se.ifmo.ru/web/guest/bcomp.jar</u>

- JRE (Java Runtime Environment) Version 8 Update 221 or newer. It can be downloaded using this link: <u>https://java.com/ru/download/</u>.

## 1. The Basic Computer model

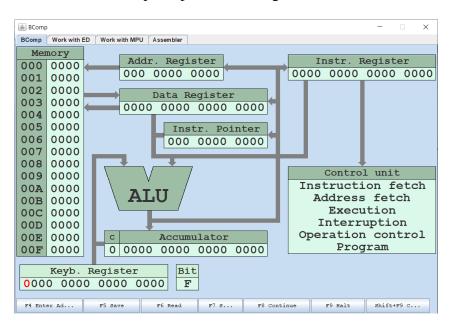

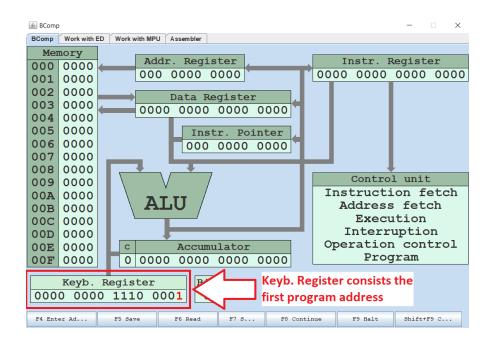

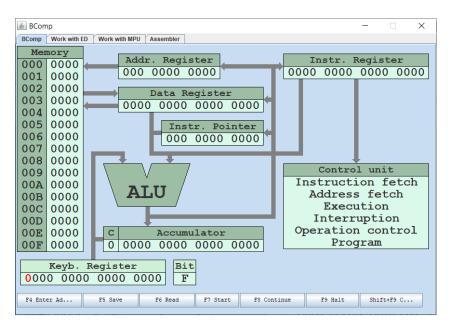

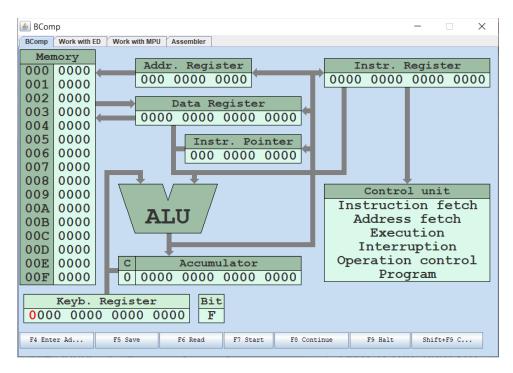

### 1.1 Purpose and description of the Basic Computer model

Basic Computer is a simple hypothetical machine that has the typical features of many specific computers. Awareness what parts a basic computer has and how it functions is quite useful for the development of microprocessor systems of any type. This is the reason why it is called a basic computer. It is highly advisable to start studying computers with a low-level machine.

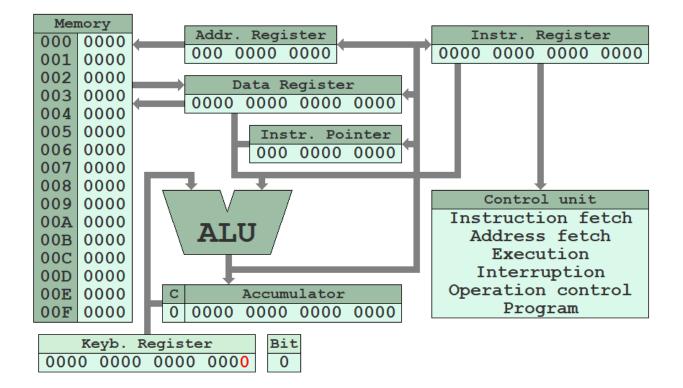

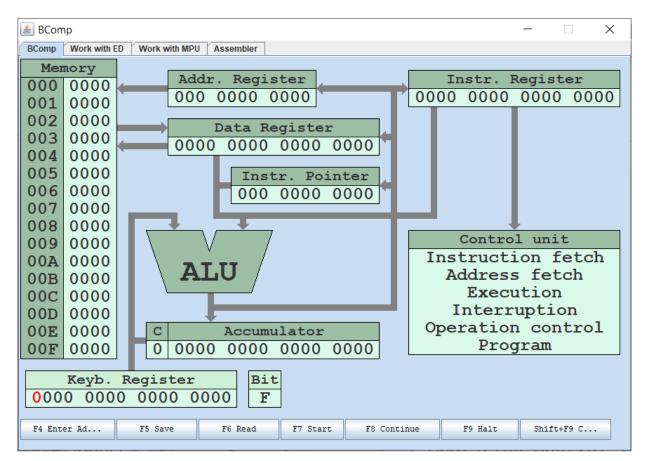

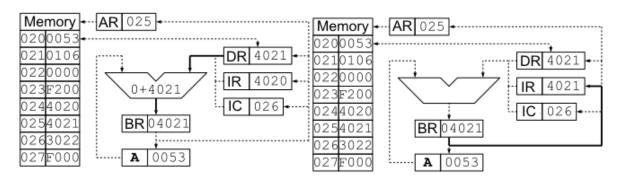

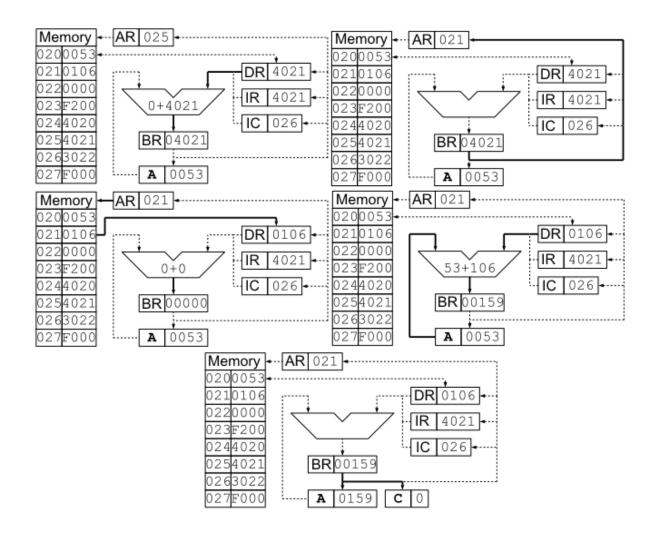

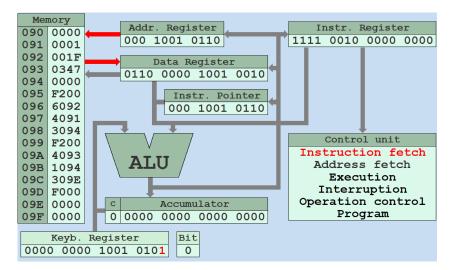

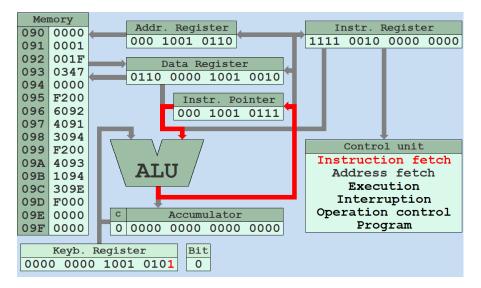

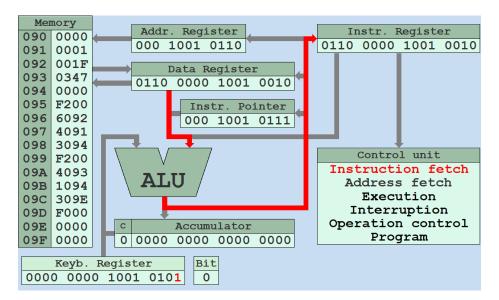

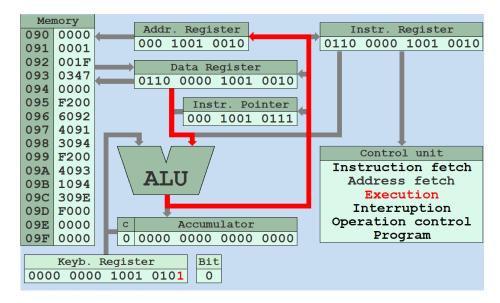

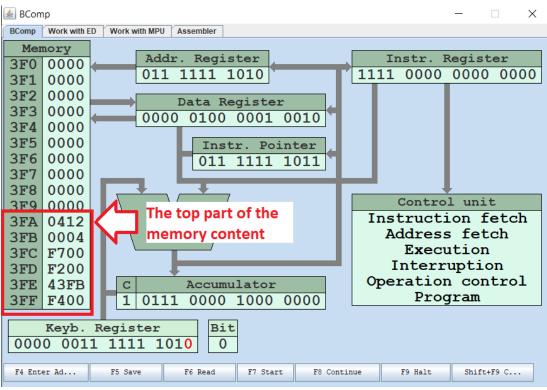

Figure 1 shows the simple structure of a basic computer. It is a unicast (single-address) computer of accumulator type, it works with 16-bit words. It implements two types of addresses: direct and indirect. The smallest addressable unit is a word that consists of eight bits or one byte.

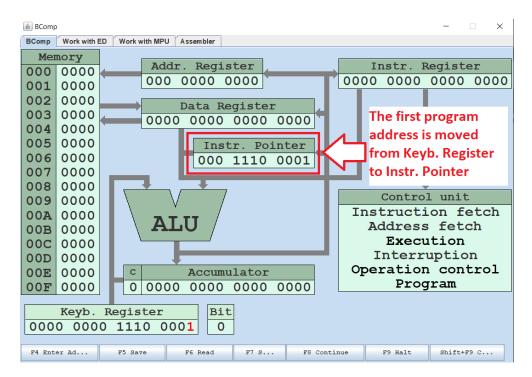

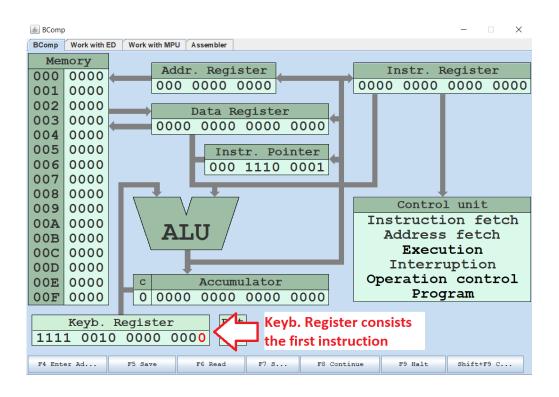

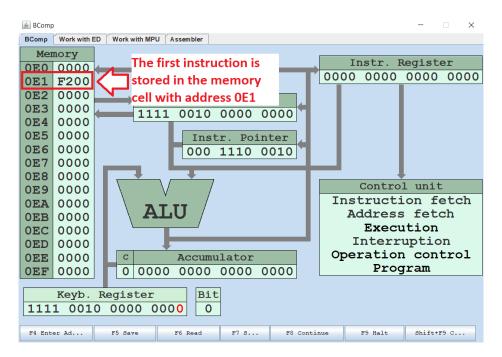

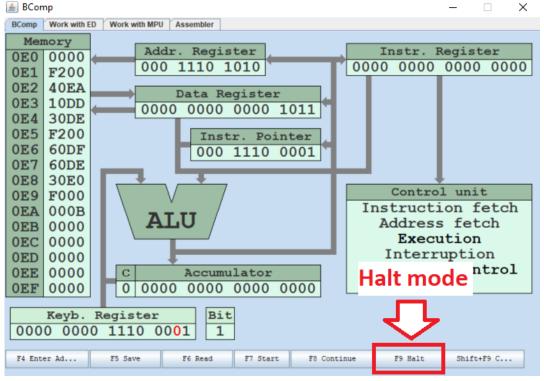

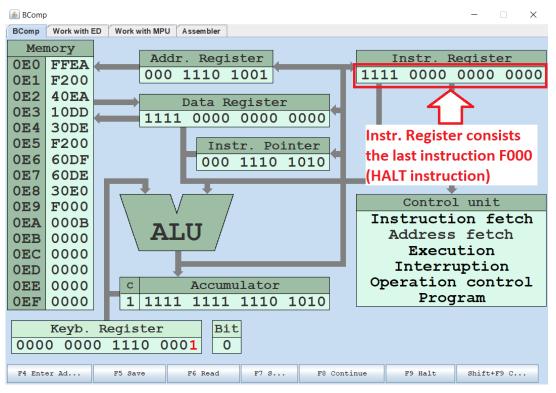

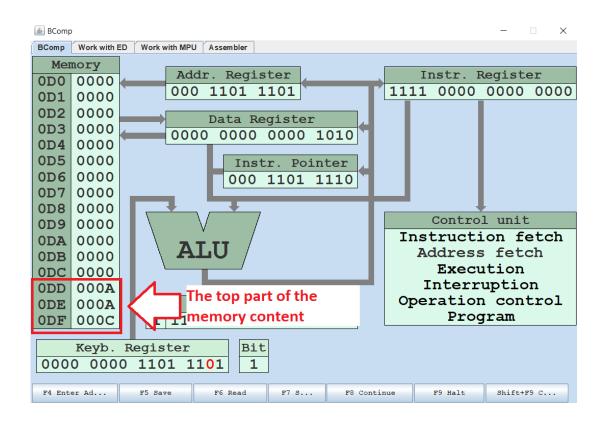

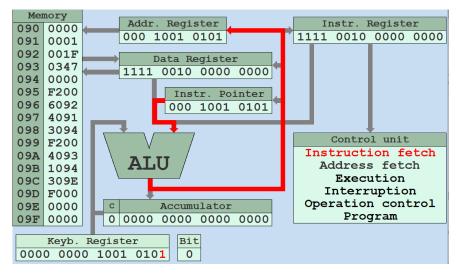

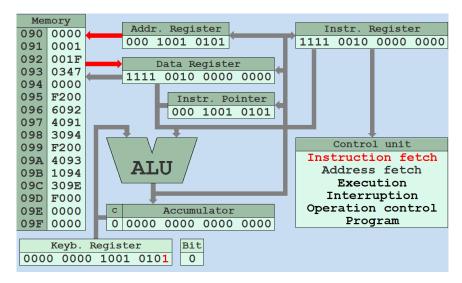

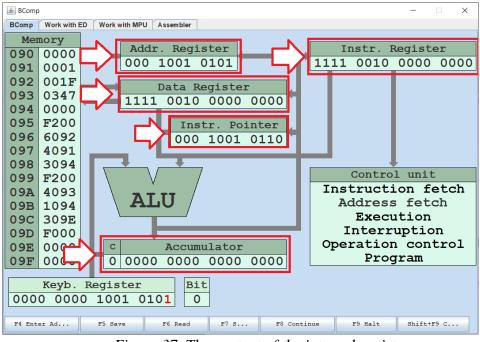

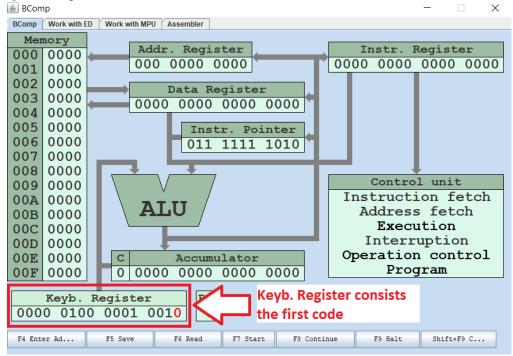

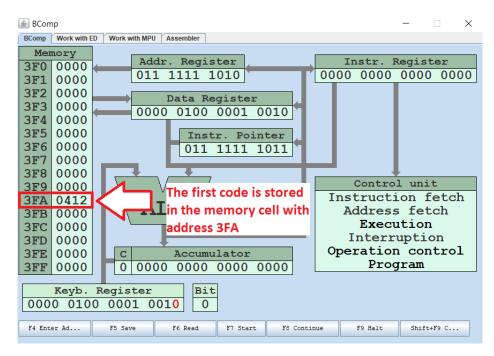

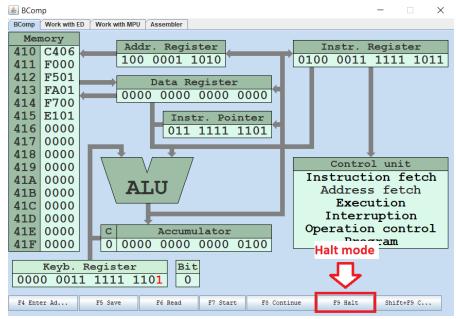

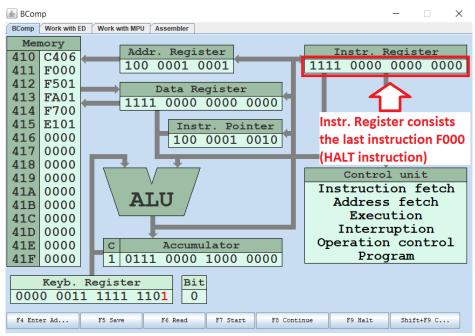

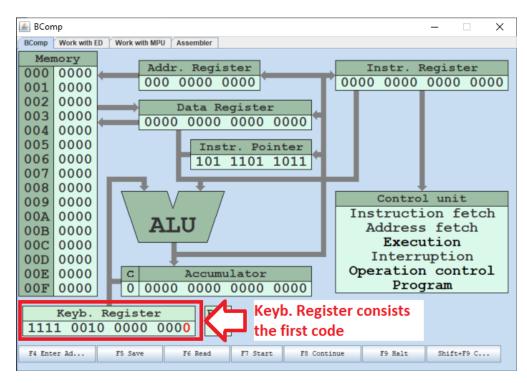

Figure 1. The Basic computer model

Consider the components of Basic Computer:

- Memory consists of 2048 cells (1 cell = 16 bit). These cells have addresses from 0 to 2047. A hex address range 008 to 00F are index cells. They are intended for addressing mode organization, usually, they are useful in loops.

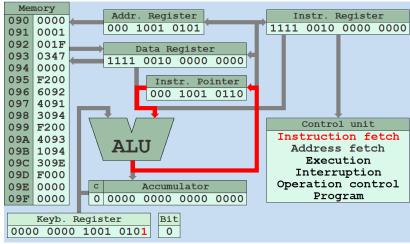

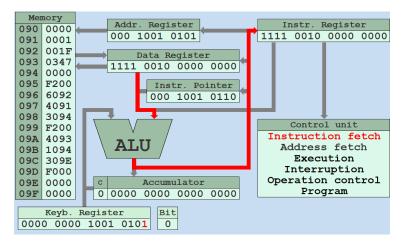

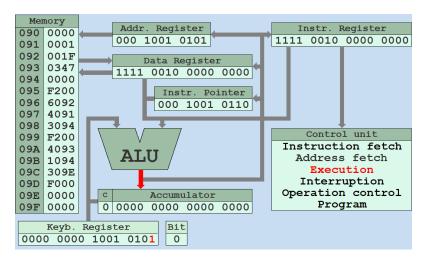

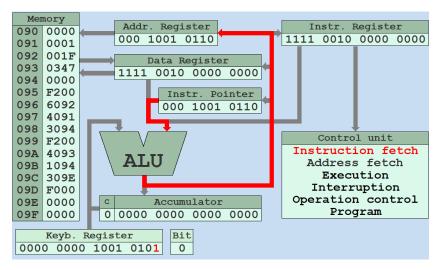

- **The Processor** consists of several registers, an arithmetic and logic unit, and a control unit.

- Arithmetic and logic unit (ALU) usually performs arithmetic operations, such as addition and addition-with-carry. A carry can be obtained as a result of the previous operation, which is the operation of logical multiplication and inversion. All transfers between registers are also performed via the ALU.

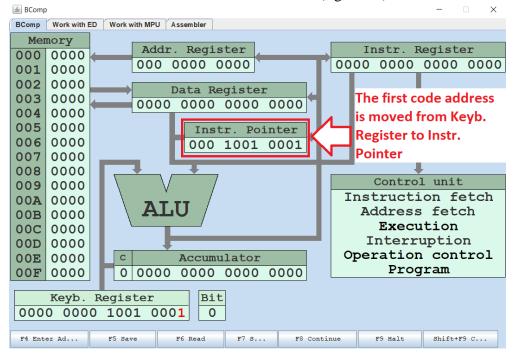

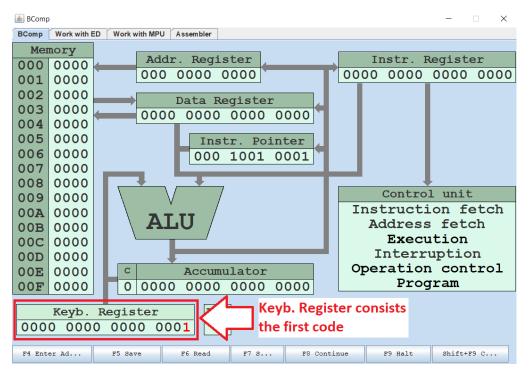

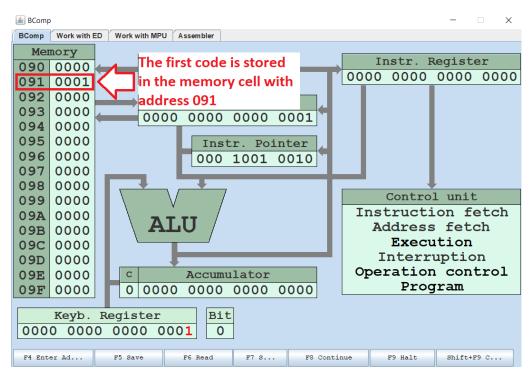

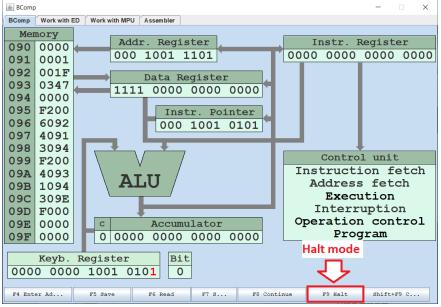

- **Instruction Pointer** (IP) is a register, that stores the address of a memory cell, which contains the address of the next command to be executed. The length of IP is 11 bit, so it

allows to address 2048 memory cells. In literature this register can be also referred as the program counter.

- Address register (AR) also has 11-bit length. It contains the address of the memory cell accessed by the processor.

- **Instruction register** (IR) has 16-bit length. It stores the code of the currently executing command.

- **Data register** (DR) has 16-bita length. It is used for temporary storage of 16-bit words during the exchange of data between the memory and the processor.

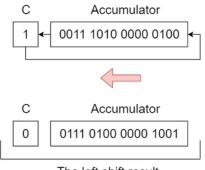

- **Buffer register** (BR) has 17-bit length. It is used for temporary storage of calculation results from ALU. This register is also used when performing shifts.

- Accumulator (A) is a 16 -bit register. One operand for arithmetic and logic operations is in the accumulator; the second one is in the data register. The intermediate result is stored in the accumulator register.

- **One-bit registers (flags)** are useful for both arithmetic and logic operations:

- **Carry flag** (C) is a flag register used to indicate when an accumulator register is overflowed.

- $\circ$  Zero flag (Z) is a single-bit register. It is set to 1 or true, if an arithmetic result in the accumulator register is zero or otherwise it resets.

- Sign flag (N) stores a number sign value from the accumulator register, it is a duplicate of the fifteenth bit of this value.

#### **1.2 Basic Computer instructions**

The basic computer can execute the predefined instruction set. While writing a program, a user is limited by these instructions. The basic computer instructions can be divided into three groups depending on blocks they refer to.

- address instructions;

- no-address instructions;

- input/output instructions.

<u>Address instructions</u> command the machine to perform actions with a memory location which address is specified in the address part of the instruction.

<u>No-address instructions</u> perform various actions without reference to a memory location.

For example, the CLA instruction (Table 1) commands the basic computer to clean the accumulator register (write a zero-code into A). This is an instruction to process an operand, which is located in a specific place. The machine "knows" the place, so the address is not needed. Another example of no-address instruction is the HLT instruction.

<u>I/O instructions</u> control the exchange of data between the processor and external computer devices.

A complete list of basic computer instructions is given in Table 1.

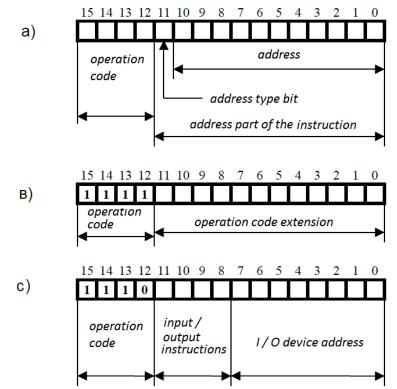

Instruction formats and addressing mode.

The developers of the computer choose three formats of 16-bit (single-word) commands with a 4-bit operation code (figure 2). In memory access instructions, 11 bits are allocated to the address. Therefore, it is possible to directly address  $2^{11}$ = 2048 memory cells, i.e. to the entire memory of the basic computer, (which is direct addressing). In this case, the address type bit should contain 0. If 1 is set in this bit, then the address located in the address part of the command indicates the cell that contains the operand address; this is indirect addressing.

Note that when mnemonically writing instructions, indirect addressing is indicated by enclosing the address in brackets. For example, the instruction ADD (25) means to add the contents of A to the content of the cell which address is stored in cell 25 (indirect addressing).

Figure 2. Instruction formats: a - address; b - no-address; c - i/o instructions

#### **1.3 Representation of integers in Basic Computer**

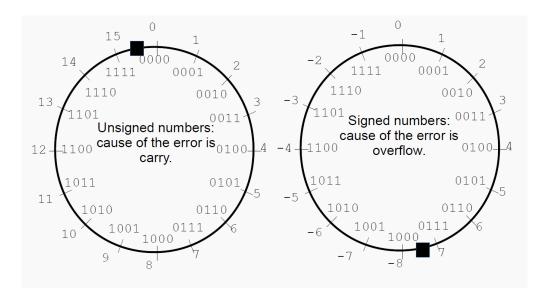

Unsigned binary integers can be used to represent zero and positive integers. Placing such numbers in one 16-bit word, they can vary from  $(0000\ 0000\ 0000\ 0000)_2 = (0000)_{16} = 0$  to  $(1111\ 1111\ 1111\ 1111)_2 = (FFFF)_{16} = 2_{16} - 1 = 65535$ . This value representation is called a direct number code.

Such values (signed binary numbers) are fixed-point numbers that separate the integer and fractional parts of a number. In the numbers used in the basic computer, the position of the decimal point is strictly fixed after the least significant bit of the word.

The signed binary numbers are used when distinguishing between positive and negative numbers is necessary. In modern computers, an additional code represents signed integers. The most significant bit of the format determines the sign of a number: 0 for positive numbers and 1 for negative ones. Obviously, a twos-complement form of positive number matches its direct code. To represent a negative number in the twos-complement form, the direct code of the number module should be inverted (obtaining the reverse number code) and add 1 to the result. The same operation is used while changing the sign of a number represented in the twos-complement form.

(M), (A), (IP), (C), (B) – the content of a cell, where the address is memory, accumulator, the instruction pointer, carry register, data register and I / O devices with address B.

XXX – memory cell address.

XX - I / O device address.

## Table 1. Basic computer instructions